CFBを用いた「薄膜チップレット」によるアナログICの積層集積

本記事のリーフレット

近年、半導体は、社会や経済の基盤を支える重要な要素として位置づけられており、特に、スマートフォン、自動車、社会インフラ、防衛などの先端技術分野では、高性能半導体が欠かすことはできない。半導体の進歩は、現代社会の持続的成長の原動力の一つである。

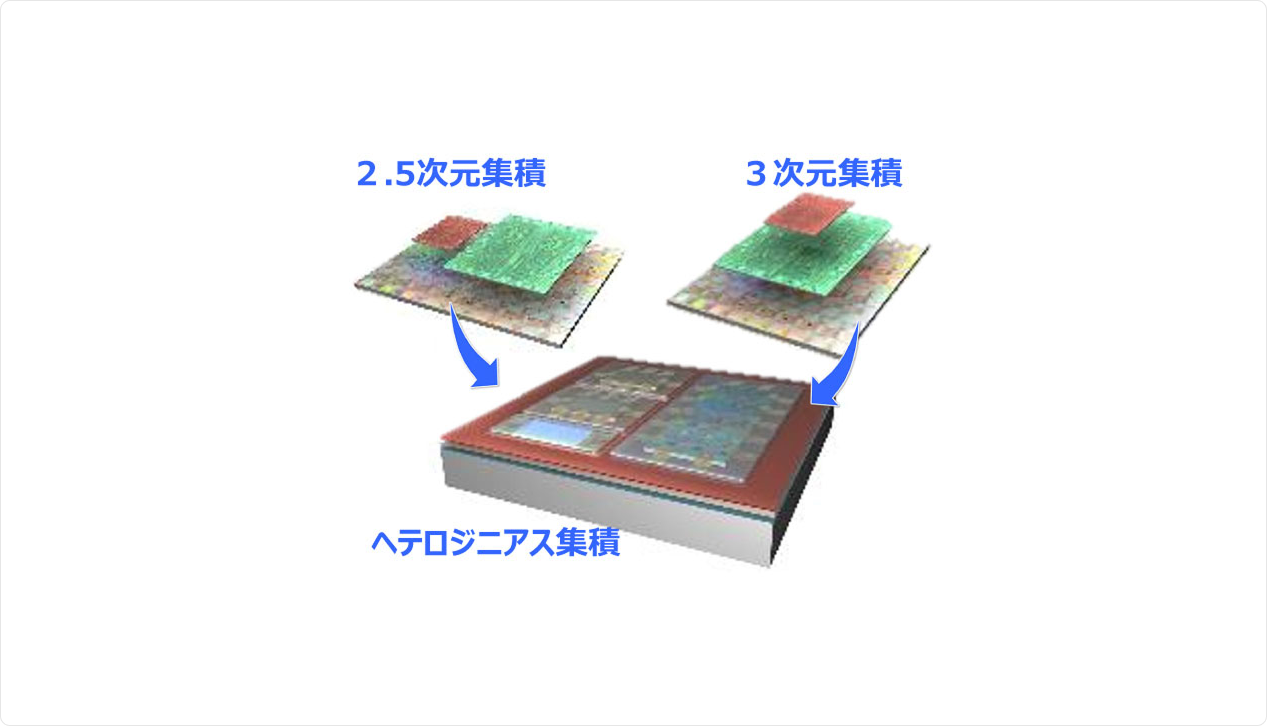

半導体の進歩は微細化により支えられてきた。しかし、物理的限界やコスト増大のため、微細化だけでなく、複合化も取り入れた新たな潮流へとシフトしている。複合化の一つがチップレット技術である。チップレット技術とは、複数の小規模な機能の半導体チップ(チップレット)を、インターポーザー(中継基板)を介して平面接続(2.5次元実装と呼ばれる)や、3次元に積み重ねて接続し大規模なシステムを構築する技術で、物理的限界やコストの課題を回避できる。さらに、異種チップを組み合わせることで、「ヘテロジニアス集積」も可能なため、新たな付加価値として注目されている。異種チップとは、たとえば異なるプロセスノード(微細加工技術の世代)や異なる製造プロセス(ロジック、メモリー、アナログIC、RF/パワー半導体など)、シリコンとは異なる半導体材料(光デバイス、次世代半導体)によるさまざまなチップのことである。多様な異種チップを一つのパッケージに集積できれば、これまでは実現できなかった大規模で高機能な複合システムを構築できる。

OKIは、薄膜化したLEDとICチップを接合して3次元集積する独自のCFB(Crystal Film Bonding)(注1)技術を用いて「ヘテロジニアス集積」を実現し、2006年に世界に先駆けて量産に成功した(参考文献1)。以来、LED素子の出荷実績は1,000億ドットを超え、量産信頼性の高いコア技術として確立している。

CFB技術をLEDだけでなく、さまざまな結晶材料やデバイスへ拡張し、半導体デバイスの付加価値向上に貢献する取組みが「CFBソリューション」である。現在、マイクロLED、フォトニクスデバイス、パワーデバイス、そして、本稿で紹介するアナログICの分野で開発を進めている。

本稿では、アナログICの従来チップレット技術による集積の課題を説明し、日清紡マイクロデバイス株式会社殿のアナログICとOKIのCFBを用いた「薄膜チップレット」技術を紹介する。

アナログICのチップレット技術の課題

アナログICは、センシングした物理現象(温度、音、光、圧力など)を電気信号に変換し、デジタルICで扱いやすい形に増幅して整える重要な役割を担う。チップレット技術の中でも、特に異なったチップを積層する3次元実装集積は、アナログICに単純な小型化以外にも多くのメリットをもたらすと予想される。たとえば、集積するICのプロセスノードを個別に選択することでコストと特性の最適化が図れるほか、短い配線長によって電気抵抗が低下し、高速化や発熱の抑制が期待できる。しかし、現状ではアナログICの3次元集積はデジタル半導体ほど進んでいない。その主な課題は以下の2点である。

課題1

3次元集積の最も一般的な方法はTSV(Through Silicon Via)(参考文献2)である。TSVは、シリコン基板に直径数µm~30µm程度、深さ100µm程度のアスペクト比の大きいビアを高密度に配置するため、非常に高度な製造技術と精密な装置が求められる。ビアの形成には高温プロセスや特殊なエッチング、導電材料などの充填技術が必要で、12インチの大口径ウエハープロセス用に最適化されている。一方アナログICは、基板径8インチサイズ以下のレガシープロセスでの製造が一般的である。比較的低温でシンプルな装置が使用されるため、精密な加工技術を適用することは難しく、汎用的でない高度な製造装置を導入する必要があり、ラインの構築に膨大なコストがかかる。従って、レガシープロセスでも実現可能な3次元集積の開発が求められている。

課題2

アナログICはデジタルICに比べ、連続的で高電圧の信号を用いるため、積層した回路同士の電気信号の干渉によるノイズ(クロストーク)が発生しやすい。デジタルICの電圧範囲は一般的に1V~5Vであるが、たとえば、オーディオアンプに印加するアナログ信号の電圧は数十Vに達することがある。このような高電圧環境下ではクロストークの低減が課題となる。

本稿の目的は、レガシープロセスの課題1と課題2を解決した、アナログICを含む大規模な複合集積システムを実現するための新たなチップレット技術の提案である。

アナログICの3次元積層を実現可能なCFBは、課題1に対して有望な手段であるが、ICの薄膜化により回路同士がより近接し、課題2のクロストークの問題が顕著になることが予想された。この課題解決を、共創パートナーである日清紡マイクロデバイス株式会社殿とのコラボレーションにより実現できた。

共創パートナーの紹介

日清紡マイクロデバイス株式会社殿は、高音質のオーディオや車載を始めとした多様なアプリケーション向けにアナログIC製品を提供している。スマート社会の発展に伴い、IoT機器などの通信装置が増加し、周囲から受けるノイズの影響も増大している。同社もこうしたノイズ問題への取組みを行っている(参考文献3)。同社は、長年培ってきたアナログ技術により、ノイズ遮蔽構造(シールド)を必要なエリアに配置する「局所シールド」の設計技術をもち、高精度なローノイズアナログICを提供している。

本稿の開発では、この局所シールドが導入されているアナログICを使用し、CFBによる薄膜ICの3次元実装で課題となるクロストークを解決した。

共創成果

本章では、アナログICのCFBによる「薄膜チップレット」開発の成果を説明する。

(1)実証① ガラス基板上接合によるCFB有効性の実証

本実証実験では、接合先の基板に透明のガラス基板を用いてIC on Glassとし、裏面からの接合外観および薄膜ICの動作確認を行った。

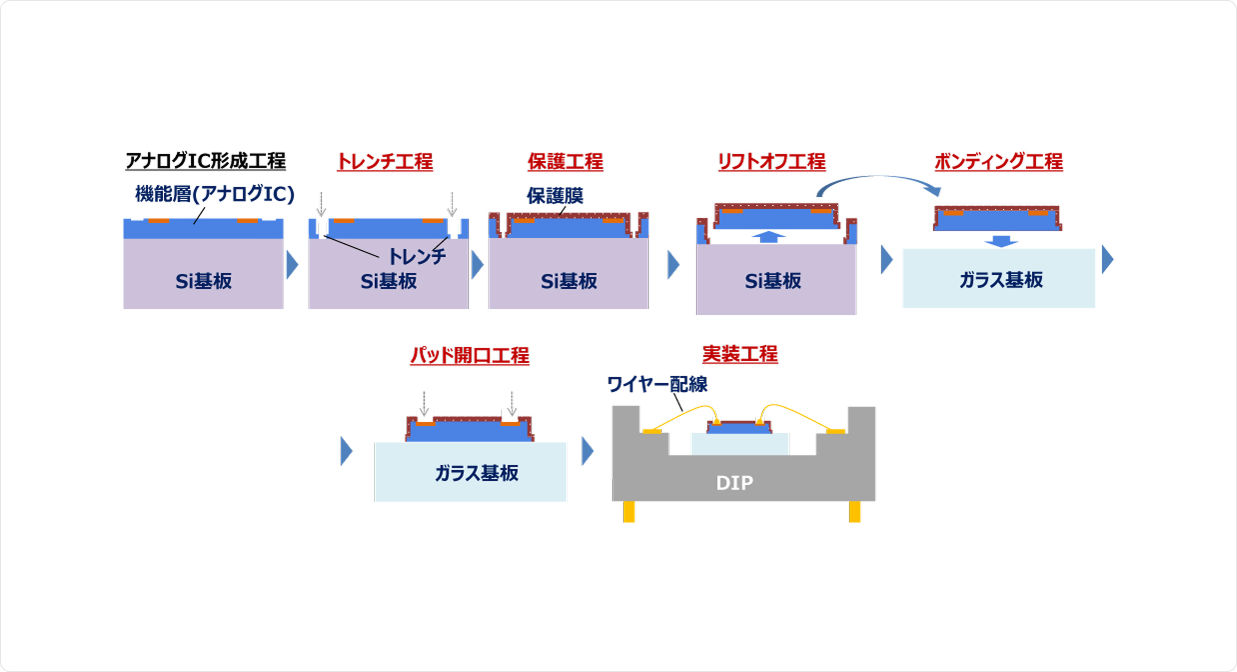

薄膜化したアナログICは、Si(シリコン)基板上に多くのトランジスタを含む素子が半導体プロセスにより形成され、オーディオ向けオペアンプとして動作するものである。チップサイズは約2mm×1.5mmであり、Si基板を含めた厚みは数百µmである。しかし、実際にアナログICとして動作する部分(以下、機能層)の厚みはわずか数µmである。このアナログIC向けに今回新たに開発したCFBプロセス(図1)を以下に説明する。

トレンチ工程では、アナログIC機能層の周囲をフォトリソグラフィおよびドライエッチングにより、Si基板に至るまで溝を形成した。

保護工程では、トレンチ工程で分離したIC機能層周囲を覆うように保護膜を形成した。

リフトオフ工程では、IC裏面のSi基板を除去しアナログICの機能層をリフトオフする。保護膜によりリフトオフ中の浸食ダメージを防止し、構造を保ったまま薄膜アナログICとしてリフトオフに成功した。

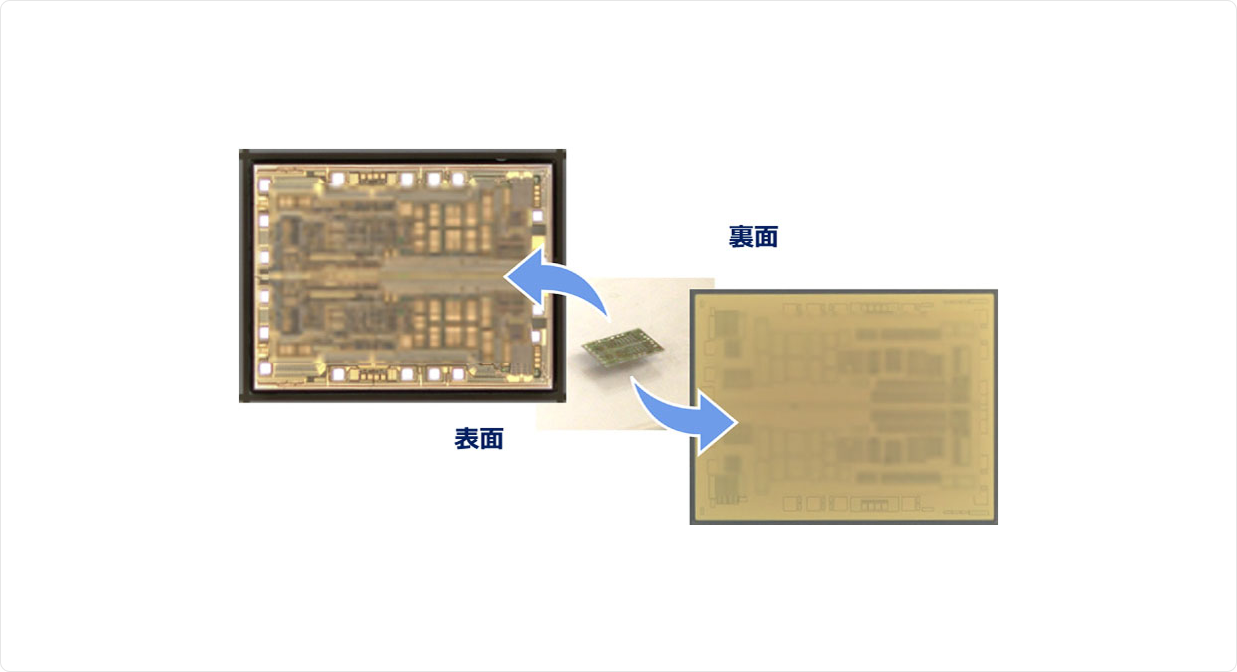

ボンディング工程では、リフトオフした薄膜アナログICをガラス基板上に分子間力接合した。ガラス基板の上面(表面)側も下面(裏面)側共に損傷はなく、接合部分には気泡もなく、良好に接合されていることが確認できた(図2)。

パッド開口工程では、保護膜の一部をフォトリソグラフィおよびドライエッチングで除去し、ICに動作信号を入力する電極を露出させた。このCFBガラス基板を5mm角にダイシングで小片化し、実装しやすい形状に整えた。

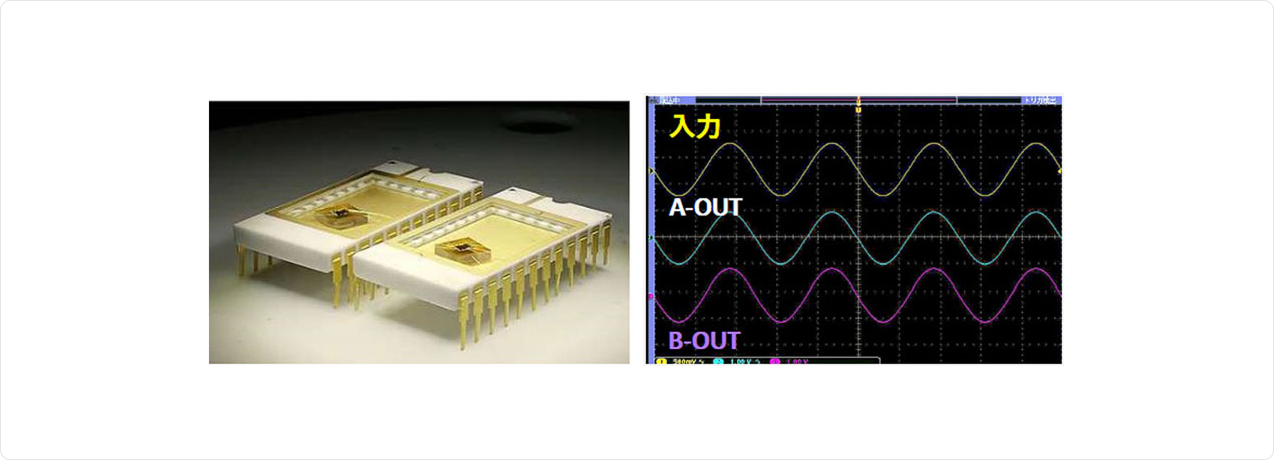

実装工程以降は、日清紡マイクロデバイス株式会社殿に実施いただいた。セラミックDIP(Dual In-line Package)に実装し、ワイヤー配線により駆動回路に接続した。

このアナログICに動作テスト用の電気信号を入力したところ、量産品と同等の入出力特性を得ることができた(図3)。さらに、実際にオーディオシステムに接続し信号増幅を行ったが、違和感のないクリアな音を再生可能であることが確認できた。以上により、多数のトランジスタを含む複雑な回路のアナログICであっても、接着剤を使用しないCFB技術により抵抗値や容量などの変化を抑制した接合ができた。すなわち、機能を損なうことなく、レガシープロセスで3次元集積が可能であることを実証できた。

(2)実証② IC上接合での動作実証

本実証実験では、積層したチップ間のクロストークの発生を検証するためにIC on ICのサンプルを作成し、動作確認を行った。接合先(下層)のICは、薄膜アナログICとは異なる設計であり、一回り大きな(約2.6×2.3mm)面積を有する高精度オペアンプである。このICには前述の局所シールドが形成されている。

まず、実証①のプロセスをベースに、トレンチ工程からリフトオフ工程までを実施し、薄膜アナログICを準備した。

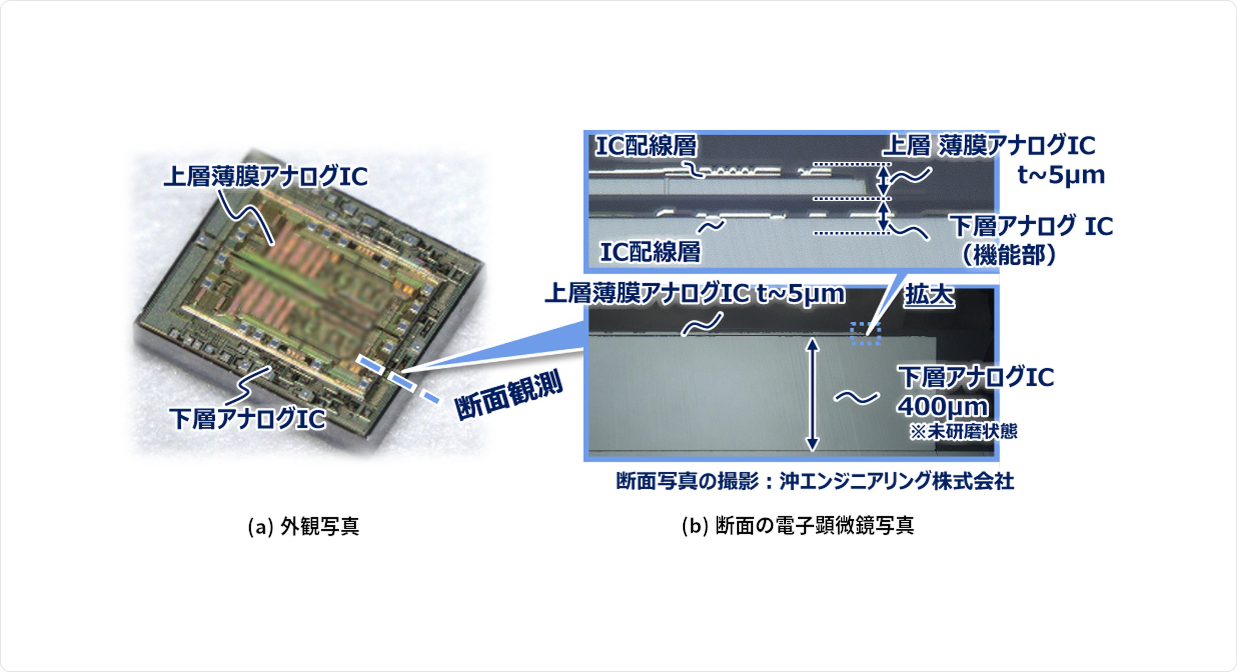

次に、下層アナログICへのボンディング工程を実施した。図4は接合後の(a)外観写真(b)断面の電子顕微鏡写真である。実証①のガラス基板とは異なり、IC表層には回路形成による数µmオーダーの凹凸がある。そのため、接着剤を使用しない分子間力接合を可能にする平坦化膜を形成した。これにより、実証①同様に薄膜アナログICを接合することに成功した。

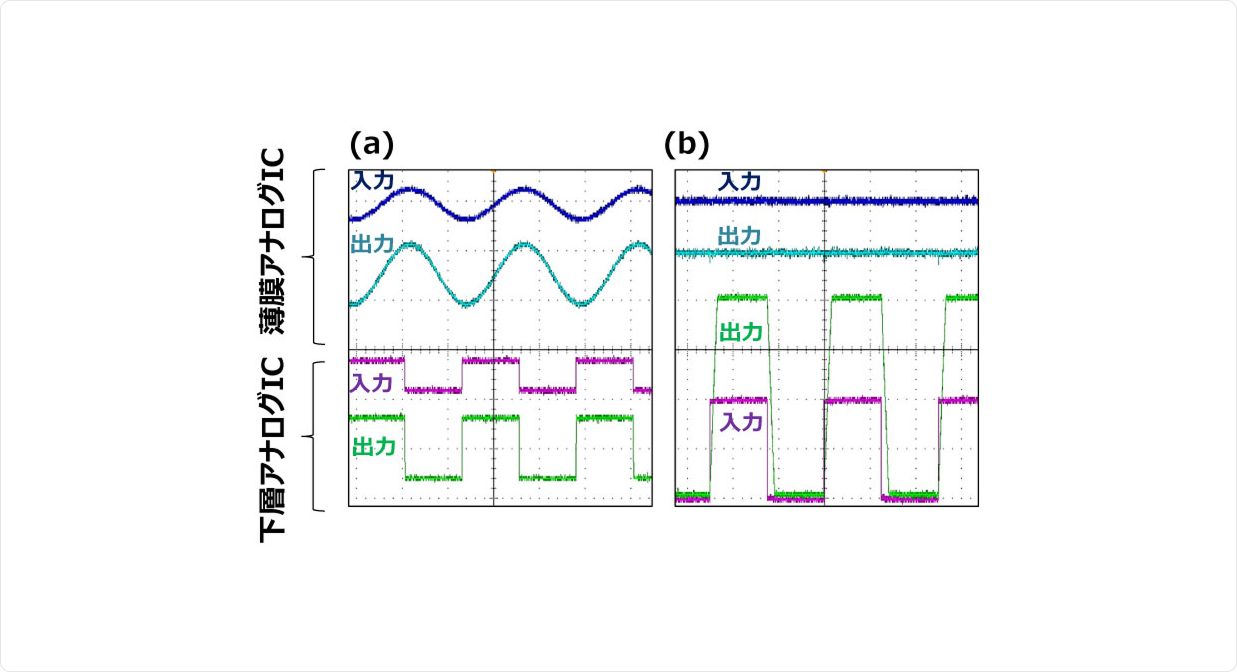

実証①同様に、パッド開口工程および実装工程を行い、特性の評価を行った。図5はテスト信号で測定した出力特性を示している。まず、下層アナログICには矩形波を、薄膜アナログICには正弦波を同時に入力した。その結果、いずれのICも仕様どおり2倍の電圧増幅特性が確認できた(図5(a))。次に、下層アナログICに比較的大きなピーク電圧(10V)の矩形波を入力し、薄膜アナログICは0V(オフ状態)とした。その結果、下層アナログICは同様に仕様どおり2倍の電圧増幅特性が得られ、薄膜アナログICの出力は影響を受けることなく0Vであることが確認できた(図5(b))。そのほかにも消費電流や入力オフセット電圧など主要特性を測定したが、2種類のチップを単体で動作させた場合と顕著な違いはなかった。これにより、課題2を解決した3次元集積が可能であることを実証した。

薄膜チップレットの今後の展開

実証①、実証②により、CFBによる薄膜チップレットが実現できることを示し、アナログIC集積技術の発展の可能性が飛躍的に拡大した。10µm以下の薄膜であることから、CFB後の基板も一般的なフォトリソグラフィが可能で、たとえば薄膜端部の乗り越え配線によりIC間を接続することができ、プロセスノードを問わない複合化が可能である。全体のチップ厚も下層アナログIC単体の厚さと殆ど変わらず、既存のパッケージに実装でき、市場投入もしやすい。また、アナログ半導体同士の3次元集積に限らず、面積の大きいローノイズアナログIC上に、小型化したデジタル半導体IC、センサー素子、抵抗やキャパシタなどの電子部品を2.5次元や3次元に集積した薄膜チップレットを組み合わせ、アナログデジタル混載など、小型で多機能な高度な付加価値を持った半導体デバイスにも展開できる(図6)。

まとめ

本稿では、CFBソリューションの一つとして、アナログICとOKIのCFBを用いた新技術「薄膜チップレット」を紹介した。

今後も引き続き高度なアナログIC設計技術を有する日清紡マイクロデバイス株式会社殿とコラボレーションし、応用展開を予定している。

謝辞

本開発は、日清紡マイクロデバイス株式会社殿との共創によるものです。心より感謝申し上げます。

参考文献

(参考文献1)谷川兼一、鈴木貴人、古田裕典、小西晃雄、金森広晃:接合技術で半導体デバイスの付加価値を向上するCFBソリューション、OKIテクニカルレビュー 第240号、Vol.89 No.2 p66、2022年11月

(参考文献2)東京エレクトロンデバイス株式会社:【注目】AI時代の発展を支える半導体製造技術「TSV技術」とは(外部サイト)

(参考文献3)日清紡マイクロデバイス株式会社:ノイズとアナログ半導体(外部サイト)

筆者紹介

石川琢磨:Takuma Ishikawa. グローバルマーケティングセンター CFB開発部

谷川兼一:Kenichi Tanigawa. グローバルマーケティングセンター CFB開発部

古田裕典:Hironori Furuta. グローバルマーケティングセンター CFB開発部

桑原秀治:Hideharu Kuwabara. グローバルマーケティングセンター CFB開発部

桑原恒平:Kouhei Kuwahara. グローバルマーケティングセンター CFB開発部

用語解説

- ヘテロジニアス集積

- 半導体で、異なる技術や素材を組み合わせて、一つのシステムを構築する集積技術。

- レガシープロセス

- 既存の製造技術や設備を用いた半導体製造方法。最新の技術に対して、比較的古いが安定性や信頼性に優れ、コスト効率が高いため現在も多くのアナログICで使用されている。

- オペアンプ

- アナログ信号の増幅および処理に広く用いられる電子部品。

(注1)CFBは、OKIの日本登録商標です。