COLUMN

半導体の「チップレット」とは? ― モノリシック設計との違い、実装戦略の最新動向を解説

この記事で分かること

- 従来のモノリシック設計が直面しているコスト・歩留まり面の課題

- チップレット、ダイ、先進パッケージングの2.5次元/3次元実装など基本用語の意味

- チップレット実装の課題とUCIeの最新動向

- 実装・基板技術を高度化するOKIの取り組み

半導体の進化は、これまで「ムーアの法則」に象徴される微細化によって支えられてきました。しかし近年では、先端ノードの開発・製造コストの増大により、1つの大きなチップに機能を集約する従来型の設計だけでは、限界も見え始めています。

そこで注目されているのが、機能ごとに分けた複数のチップを1つのパッケージ内で統合する「チップレット」です。

本記事では、チップレットの基本、先進パッケージングの2.5次元/3次元実装やUCIeの動向、さらに実装・基板技術の重要性を整理しながら、OKIの取り組みも紹介します。

目次

従来の半導体設計が直面している「限界」と「変化」

半導体市場は拡大を続けています。世界半導体市場統計(WSTS:World Semiconductor Trade Statistics)の2025年秋季予測によると、世界半導体市場は2025年に7,722億ドル、2026年には9,754億ドルに拡大すると見込まれています。市場の成長が続く一方、先端ノードへの投資負担が大きいため、すべての機能を最先端プロセスで一体化する設計が、常に最適とは言い切れなくなっています。

これまでの主流は、1つの大きな半導体チップに機能を集約する「モノリシック設計」です。一体設計がしやすい反面、チップが大きくなるほど製造上の難易度が増します。特に高性能なロジック半導体では、機能を増やしてダイを大型化すると、歩留まりやコストの面で不利になりやすくなります。

従来設計が直面しやすい課題は、主に次の3点です。

- 先端プロセスの開発・製造コストが高い

- ダイの大型化によって歩留まりが下がりやすい

- 製品ごとの派生展開や設計再利用がしにくい

こうした背景から、半導体業界では従来の「1つに詰め込む」発想に代わり、「どう分けて、どうつなぐか」という考え方が、重視されるようになっています。

チップレットとは? モノリシック設計との違い

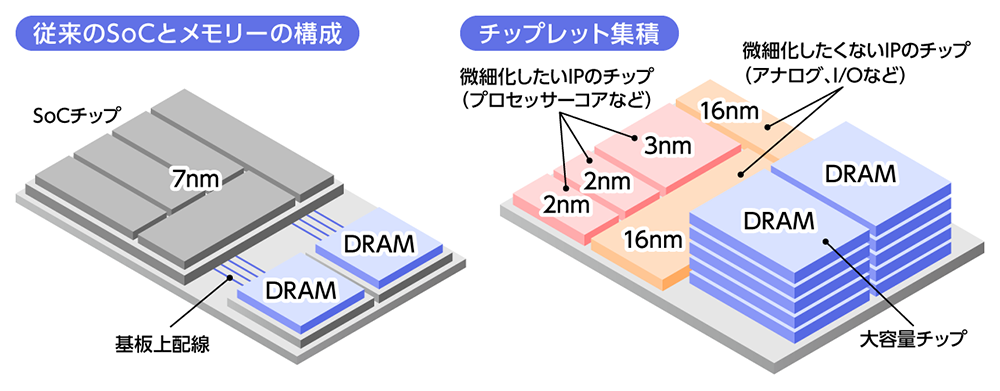

チップレットとは、半導体の機能を複数の小さなチップに分割し、1つのパッケージ内で接続して使う設計手法です。従来のモノリシック設計が1つの大きなチップに機能を集約するのに対し、チップレットは演算、I/O、周辺回路などを分けて構成できる点が特徴です。

ダイとは、ウエハーから切り出された個々の半導体チップのことです。チップレットは、従来1つの大きなダイにまとめていた機能を、小さなダイに分割し再統合する考え方です。

両者の違いを整理すると、次の通りです。

モノリシック設計:1つの大きなダイに機能を集約する方式です。構造を一体で設計しやすい反面、ダイが大きくなるほど歩留まりやコストの負担が大きくなりやすい点が課題です。

チップレット設計:機能ごとにダイを分けて作り、1つのパッケージで統合する方式です。演算、I/O、周辺回路などに応じて適したプロセスを選びやすい一方で、ダイ同士をつなぐ接続や実装の設計は難しくなります。

重要なのは、チップレットが単なる「分割」ではないことです。分けたダイを高密度に接続し、1つの製品として成立させて初めて価値が生まれます。だからこそチップレットでは、半導体設計だけでなく、実装や熱設計まで含めた最適化が重要になります。

先進パッケージング:2.5次元/3次元実装がもたらすもの

チップレットを実際の製品として成立させるうえで重要なのが、複数のダイを高密度に接続する先進パッケージングです。なかでも代表的なのが、2.5次元実装と3次元実装です。

2.5次元実装:シリコンインターポーザなどの中継層上に複数チップを並べて搭載し、高密度に接続する方式です。チップ同士を近距離で接続できるため、高帯域化や高密度化に向いています。

3次元実装:チップを垂直方向に積層して接続する方式です。配線長を短くしやすく、高密度化や性能向上に有効な一方で、熱が逃げにくくなるため、熱設計の難易度は高くなります。

チップレット時代では、こうした実装技術により、従来は基板上で行っていた接続をパッケージ内部へ近づけ、高帯域化や省電力化を図る流れが強まっています。つまり、半導体の性能は前工程だけでなく、後工程を含めた実装技術にも、大きく左右されるようになっています。

標準化規格「UCIe」の展望

チップレットの活用が広がるなかで重要になるのが、異なるチップレット同士をどう接続するかという標準化です。その代表的な規格が、UCIe(Universal Chiplet Interconnect Express)です。

UCIeは、異なるメーカーが製造した機能別のチップレットを、1つのパッケージ内で高速かつ低消費電力に接続するためのオープンな標準規格です。2022年にインテル、AMD、Google、TSMCなどが設立したコンソーシアム「UCIe Consortium」により策定され、AIチップおよび高性能な次世代半導体の開発を高速化・低コスト化を実現する技術として注目されています。

このUCIeの策定と普及を推進するUCIe Consortiumは、パッケージ内でチップレットを相互接続するためのオープンなエコシステム構築を目指し、2025年に標準仕様である「UCIe 3.0 Specification」を公表しています。

今後、UCIe対応製品の普及が進めば、サーバープロセッサーやAIアクセラレーター、GPUなどにおいて、異なるチップレットを組み合わせる設計が広がる可能性があります。中長期的には、メーカー間でチップレットを選択・統合する仕組みが整い、半導体開発の分業が進むことも期待されます。さらに、光接続や新しいコンピューティング技術との組み合わせにより、チップレット活用の幅は一段と広がっていくと考えられます。

実装の高度化を阻む壁と「熱設計」の重要性

チップレットや3次元実装の議論で見逃せないのが、実装の難しさです。複数ダイを近接配置したり、垂直に積層したりすると、熱、電源供給、信号品質、機械的信頼性、テスト工程など、実装段階で考慮すべき要素が一気に増えます。なかでも熱は、性能と信頼性を左右する重要なテーマです。熱がこもりやすくなると、安定動作や性能維持が難しくなります。

実装で重要になる観点は、主に次の通りです。

- 熱拡散とホットスポット対策

- 高速信号の品質確保

- ビア構造や配線設計の最適化

- 電源・グランド設計の安定化

- 量産を見据えたテスト容易性

これに伴い、基板設計の重要性も増しています。パッケージ内部の接続だけでなく、その先につながる基板側でも、高速伝送、インピーダンス制御、ビア構造の最適化が求められます。

チップレット時代では、半導体そのものの設計だけでなく、実装、基板、熱、シミュレーション、評価までを含めて最適化する視点が重要になります。

実装・基板技術を高度化するOKIの取り組み

こうした実装高度化の流れに対し、OKIグループでは、基板、シミュレーション、生産体制の各面から技術強化を進めています。

高周波ビア高精度シミュレーション技術を開発

OKIグループでプリント配線板の開発・製造を担うOKIサーキットテクノロジーは、次世代AIデータセンターを支える1.6Tbpsクラス高速伝送PCBに向けに、「高周波ビア高精度シミュレーション技術」の開発に成功しました。高周波化により顕在化する多層PCBのビア特性制御を、自社製造プロセスを考慮したシミュレーションベース設計で実現し、開発期間の短縮に貢献しています。

最先端半導体対応の超高多層プリント配線板製造ラインを新設

OKIサーキットテクノロジーでは、AIやデータセンター、次世代通信網などに使用される最先端半導体の製造・検査装置に搭載する超高多層プリント配線板の回路形成ラインを、上越事業所に新設しました。新ラインでは、ビアピッチ0.23mmに対応可能な高精度・高精細回路形成を実現し、従来比約1.4倍の生産能力と多品種少量生産対応力を強化しています。

CFB技術による薄膜アナログICの3次元集積に成功

OKIは、日清紡マイクロデバイス株式会社と共同で、CFB(クリスタル・フィルム・ボンディング)技術を用いた薄膜アナログICの3次元集積に成功しました。あわせてOKIは、新たに「薄膜チップレット技術」を開発しています。この技術は、機能ごとに小片チップへ分割し、2.5次元/3次元実装で統合するチップレット技術の考え方を用い、ヘテロジニアス集積への応用を目指すものです。

高多層・高密度基板にも対応

OKIサーキットテクノロジーは、100層を超える高多層リジッドプリント配線板に対応しています。高Tg FR-4を用いた通常製造プロセスで100層超の高多層基板に対応し、IVH、ビルドアップ、貫通穴埋めなど、さまざまなVIA構造の組み合わせが可能です。主な適応例として、半導体テスト装置やプローブカードにも対応しています。

まとめ

チップレット技術とは、前工程の微細化だけで半導体を進化させるのではなく、機能を分けて最適に組み合わせ、実装技術で全体性能を引き上げていく取り組みです。背景には、先端ノードのコスト負担、ダイ大型化による歩留まりの制約、そしてAIやデータセンター向けを中心とした高性能化要求の高まりがあります。

OKIでは、高周波ビア高精度シミュレーション技術の開発、最先端半導体対応の超高多層プリント配線板製造ラインの新設、薄膜チップレット技術による3次元集積、高多層・高密度基板への対応などを通じて、半導体実装の高度化を支える技術開発を進めています。

ご興味のある方は、ぜひお気軽にOKIへお問い合わせください。

- 参考情報/関連リンク

PICK UP

その他の記事

TAG

キーワードから探す

RELATED ARTICLES

関連記事

CONTACT

OKI Style Squareに関するご相談・

お問い合わせはこちら