COLUMN

次世代の2nm半導体を実現する「GAA」とは? ― FinFETとの違いと最先端プロセスの実装課題を解説

この記事で分かること

- 2nm世代への移行が進む背景と市場動向

- FinFETとGAAの違い、GAAの技術的な特長

- 最先端プロセス移行で重要になる製造・実装上の課題

- 2nm世代の高度な要求に応えるOKIの先端実装技術

半導体の微細化は2nm(ナノメートル)世代へ進みつつあり、トランジスタ構造も大きな転換点を迎えています。そこで注目されているのが、FinFETに代わる次世代構造として採用が進むGAA(Gate-All-Around)です。

本記事では、GAAの基本、FinFETとの違い、2nm世代で重要になる実装・基板技術を整理しながら、OKIの取り組みも紹介します。

目次

高まる最先端プロセスへの投資と構造刷新の必然性

急拡大を続ける半導体市場。そのなかでも、AIやデータセンター需要を背景に、とくに成長を牽引しているのがロジック半導体です。世界半導体市場統計(WSTS:World Semiconductor Trade Statistics)の2025年秋季予測では、ロジック市場が2025年に前年比37%増、メモリー市場が28%増とそれぞれ上方修正されており、2026年もデータセンター投資を背景に、ロジックとメモリーの高成長が続くと見込まれています。

市場成長をけん引する中核のひとつが、人工知能(AI)やデータセンター、自動運転、次世代通信などで使われる先端ロジック半導体です。

データの演算や制御を担うデジタル半導体であるロジック半導体のうち、一般に7nm(ナノメートル)以下の極めて微細な製造プロセスを採用し、AI処理やデータセンターといった高度なコンピューティングに特化した高密度・高性能なカテゴリーを「先端ロジック半導体」と呼びます。

このような半導体の微細化が進む一方で、従来のトランジスタ構造をそのまま縮小するだけでは、性能向上と低消費電力化の両立が難しくなっています。これまで主力だったFinFET(Fin Field-Effect Transistor)は、長年にわたり微細化を支えてきた重要な構造ですが、次世代では、電流制御や電力効率の点で課題が顕著になります。

そこで、トランジスタ構造そのものを見直す方法として注目されているのが、GAA(Gate-All-Around)です。

2nm(ナノメートル)世代への移行は、単なる線幅縮小ではありません。性能、消費電力、歩留まり、製造難易度をどうバランスさせるかという観点から、トランジスタ構造の刷新が求められています。

GAAとは? FinFETとの違い

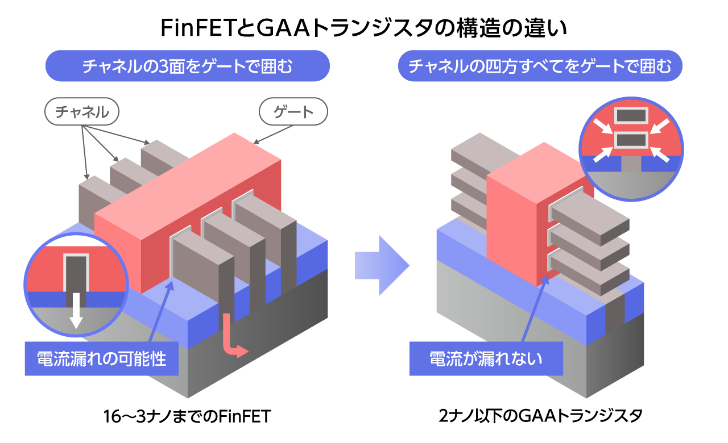

GAA(Gate-All-Around)とは、電流を制御する「ゲート」が、電流の通り道である「チャネル」の周囲を取り囲むトランジスタ構造です。微細化が進むなかでも、チャネルをより細かく制御しやすいため、次世代の先端プロセスで採用が進んでいます。

これに対してFinFET(Fin Field-Effect Transistor)は、フィン(ひれ)のように立ち上げたチャネルを、ゲートが囲む構造です。従来のプレーナ型トランジスタに比べ電流制御性が高く、長年にわたって微細化を支えてきましたが、さらに微細化が進むと、電流漏れ(リーク電流)の抑制や電力効率の改善が難しくなってきます。

両者の違いを整理すると、次の通りです。

| FinFET | GAA | |

|---|---|---|

| 基本構造 | フィン状のチャネルをゲートが囲む | チャネルの周囲をゲートが取り囲む |

| 電流制御 | 高いが、微細化が進むほど難易度が上がる | より高い制御性を確保しやすい |

| リーク電流抑制 | 微細化が進むほど難しくなる | 抑えやすい |

| 低消費電力化 | 限界が見え始めている | 進めやすい |

| 性能向上 | 微細化で対応してきた | 先端世代で有利とされる |

| 課題 | さらなる微細化で制御が難しくなる | 構造が複雑で製造難易度が高い |

GAAのポイントは、単に新しい形を採用することではなく、微細化が進んでも電流を制御しやすく、性能と消費電力のバランスを取りやすいことにあります。2nm世代では、こうした構造上の違いが、半導体の性能を左右する重要な要素となります。

GAA採用で何が変わるのか

GAAが注目されている理由は、先端プロセスで求められる高性能化と低消費電力化を両立しやすいからです。AIやデータセンター向けの半導体では、演算性能を高めつつ、発熱や消費電力を抑えて安定動作させることが求められます。GAAは、こうした要求に応えやすい構造です。

ただし、GAAはメリットだけではなく課題もあります。構造が複雑になる分、製造プロセスの難易度は上がるため、2nm世代で重要なのは、GAAの構造上の利点を活かしながら、量産性や歩留まりをどう確保するかです。

GAAの主なメリットは、次の通りです。

- 電流を制御しやすい

- リーク電流を抑えやすい

- 性能向上を図りやすい

- 2nm世代の先端プロセスと相性がよい

一方で、GAAには次の課題もあります。

- 構造が複雑になる

- 製造プロセスの難易度が上がる

- 量産時の歩留まり確保が難しい

GAAは性能と電力効率の両立に有効な一方で、その価値を製品として引き出すには、製造や量産まで含めた最適化が欠かせません。

最先端プロセスの実装を阻む「製造・コスト」の壁

GAAによる2nm世代の実現は、性能面では大きな前進ですが、製造現場には新たな課題も生みます。微細化が進むほど、製造装置、工程制御、材料、検査のすべてにおいて高い精度が求められます。

主な課題は、次の通りです。

- 微細な回路形成に対応する製造装置への大規模投資

- 複雑化する積層・形成プロセスに対する歩留まり確保

- 高密度化に伴う放熱設計の難しさ

- 低電圧動作を支える電源品質の確保

- 高速信号を安定して伝送するための実装最適化

つまり、2nm世代の価値を引き出すには、前工程だけでなく、チップそのものの進化に加え、それを載せるパッケージや基板、さらに熱・電源・信号品質まで含めた、実装全体の最適化が必要になります。

実装・基板技術の重要性

GAAによる2nm世代の実現は、性能面では大きな前進である一方、製造現場や実装現場には、これまで以上に高いハードルを突きつけます。微細化が進むほど、チップそのものだけでなく、それを支える製造装置、工程制御、実装技術の重要性も高まります。

主な課題は、次の通りです。

- 製造装置への投資負担が増加:2nm世代では、より高精度な回路形成に対応するため、最先端の露光装置や製造設備が必要になります。こうした設備投資は非常に大きく、先端プロセスの量産ハードルを押し上げます。

- 製造プロセスがより複雑に:GAAでは、従来よりも複雑な構造を高精度に形成する必要があります。そのため、工程管理や量産時の安定化、歩留まり確保が重要になります。

- 放熱設計が難しくなる:高密度化が進むほど、限られた面積の中に熱が集中しやすくなります。性能を引き出すには、チップだけでなく、パッケージや基板を含めた放熱設計が欠かせません。

- 電源品質の確保が重要になる:低電圧で高速に動作する先端半導体では、電源のわずかな変動も動作安定性に影響します。そのため、実装段階での電源設計がより重要になります。

- 実装全体の最適化が求められる:先端半導体の性能を十分に引き出すには、前工程だけでなく、パッケージ、基板、配線、熱、信号品質まで含めた最適化が必要です。

2nm世代の価値は、微細化そのものだけで決まるわけではありません。チップの性能を製品として引き出すには、製造と実装の両面から支える技術が欠かせません。

2nm世代の高度な要求に応えるOKIの先端実装技術

こうした最先端半導体の進化は、チップそのものだけでなく、それらを評価するための検査装置や、高速信号を確実に伝送するための基板に対しても、これまでにない高いレベルの性能を要求します。OKIグループでは、こうした先端半導体に関連する高度な要求に応えるため、基板、シミュレーション、生産体制の面から技術強化を進めています。

高精度回路形成への対応

OKIグループのプリント配線板事業を担うOKIサーキットテクノロジーは、上越事業所に最先端半導体の製造・検査装置向け超高多層プリント配線板(PCB)の回路形成ラインを新設しました。ビアピッチ0.23mmに対応可能な高精度・高精細回路形成に対応し、生産能力の向上と多品種少量生産対応力の強化を進めています。

高多層・高密度基板への対応

OKIサーキットテクノロジーは、100層を超える高多層リジッドプリント配線板に対応しています。高Tg FR-4を用いた通常製造プロセスで100層超の高多層基板に対応し、IVH、ビルドアップ、貫通穴埋めなど、さまざまなVIA構造を組み合わせることが可能です。主な適応例としては、半導体テスト装置やプローブカードがあります。

シミュレーションによる設計最適化

OKIサーキットテクノロジーは、次世代AIデータセンターを支える1.6Tbpsクラス高速伝送PCBに向けに「高周波ビア高精度シミュレーション技術」を開発しました。自社製造プロセスを考慮したシミュレーションベース設計により、多層PCBの高周波ビア特性を高精度に制御し、開発期間の短縮に取り組んでいます。

薄膜チップレット技術による3次元集積

OKIは、日清紡マイクロデバイス株式会社と共同で、CFB(クリスタル・フィルム・ボンディング)技術を用いた薄膜アナログICの3次元集積に成功しました。また、新たに「薄膜チップレット技術」を開発しています。これは、機能ごとに小片チップへ分割し、2.5次元・3次元実装で統合するチップレット技術の考え方を応用し、ヘテロジニアス集積へ展開するものです。

まとめ

2nm世代とGAA構造への移行は、単なる微細化の延長ではなく、半導体の性能と電力効率を両立するための大きな構造転換です。その価値を製品として引き出すには、半導体そのものの理解に加え、熱、信号、電源を含めた実装全体の最適化が欠かせません。

2nm世代を見据えた製品開発や、高密度実装の課題解決を進めるうえで、実装・基板技術の重要性はさらに高まっていくでしょう。

OKIグループでは、高精度回路形成、高多層・高密度基板、高周波ビアのシミュレーション技術、薄膜チップレット技術などを通じて、先端半導体を支える実装技術の高度化に取り組んでいます。

ご興味のある方は、ぜひお気軽にOKIへお問い合わせください。

- 参考情報/関連リンク

PICK UP

その他の記事

TAG

キーワードから探す

RELATED ARTICLES

関連記事

CONTACT

OKI Style Squareに関するご相談・

お問い合わせはこちら