エッジデバイスの共通化・小型化・省電力化技術

本記事のリーフレット

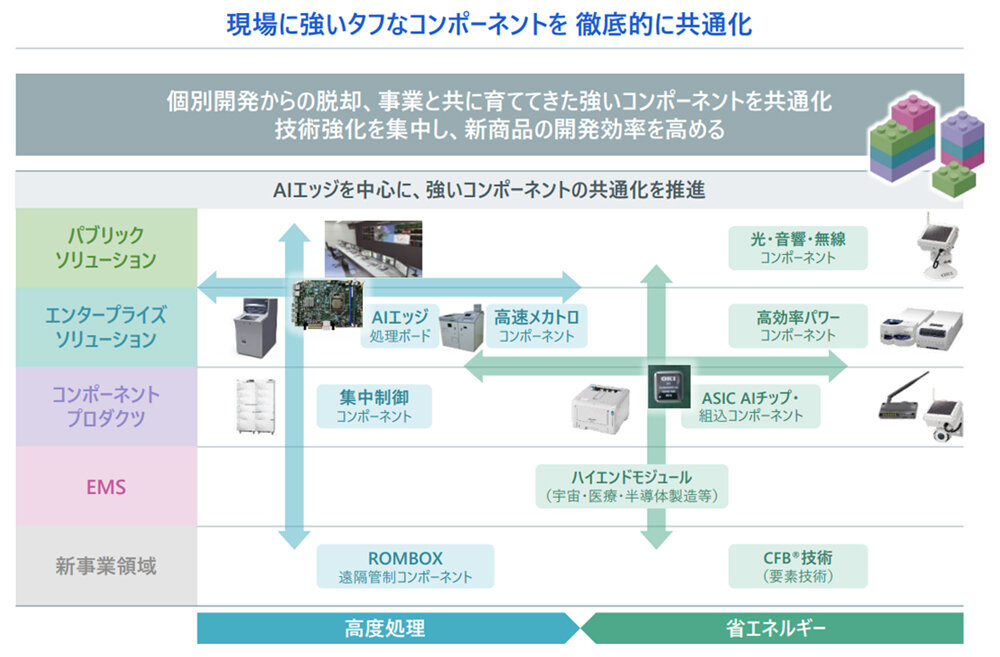

OKIでは、2023年度に発表した技術戦略において「技術強化:エッジデバイス」を重点施策として掲げ(図1)、コンポーネントの競争力強化に取り組んできた。特にエンタープライズソリューション事業製品などのエッジデバイス領域では、コア技術強化を通じて「開発生産性向上」、「多用途展開」、「省スペース・省電力化」に取り組み、個別最適設計からの脱却を目指している。本稿では、この戦略方針に基づき、エンタープライズソリューション事業向けに推進したベースアーキテクチャーの技術強化の取組みと成果を紹介する。ここでベースアーキテクチャーは、エッジデバイスで共通利用されるハードウェアとソフトウェアの両方を指す。

開発背景と目的

OKIのエンタープライズソリューション事業製品は、ATM・精算機・出納機など多様な用途やニーズに応じて個別最適設計を行い、幅広い機種展開を実現してきた。一方で、個別最適設計の積み重ねにより、以下の三つの課題があった。

・課題Ⅰ 外部要因への対応力不足

昨今の半導体不足などの部品供給リスクが高まるなか、個別最適設計への依存が製品ごとの異なる対応や部品確保を必要とし、迅速な対応を阻害していた。

・課題Ⅱ 製品開発期間の長期化

顧客要望から開発を進める際、個別最適設計が主流となることで開発の長期化を招き、市場投入時の要求変化や競合他社による先行リスクが増大していた。

・課題Ⅲ 環境対応技術の全機種展開の困難さ

低消費電力化や環境負荷低減といった技術適用に際し、個別最適設計や機種数の多さが障害となり、迅速かつ一律な展開が困難となっていた。

これらの課題に対し、市場変化・顧客要求・社会的責任に柔軟かつ迅速に対応するため、従来の個別最適設計からベースアーキテクチャーへの転換、および技術基盤を強化した。

取組み施策と技術コンセプト

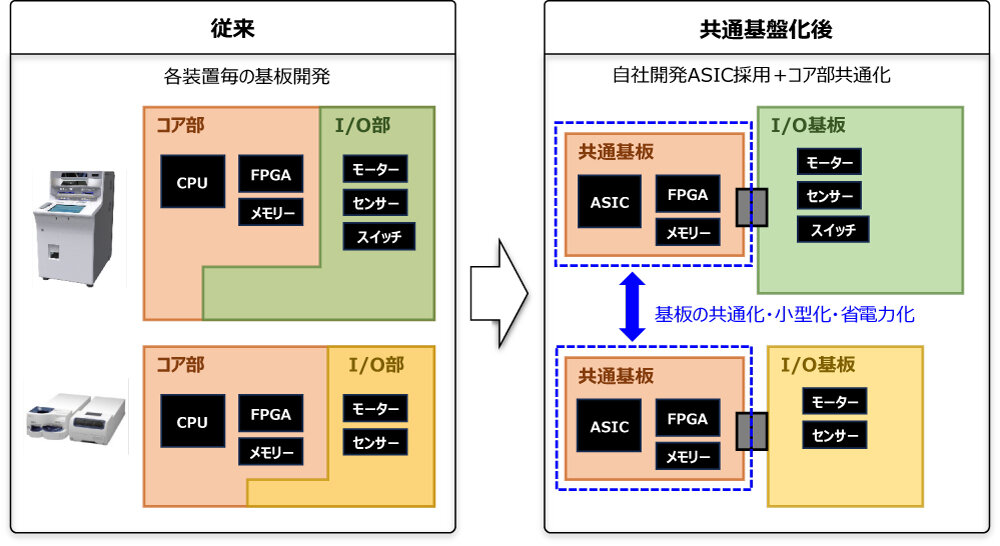

前述した課題解決に向けて、エンタープライズソリューション事業製品の共通化および基板技術の進化を推進している。従来、製品内部のメカ制御基板は、各製品の仕様に合わせて個別開発されていたが、本取組みではメカ制御基板の「共通化」を主要コンセプト(参考文献2)として掲げ、以下三つの施策に注力している。

・施策① 基板分離構成

基板機能を共通基板とIO基板に分離する構成を採用する。これにより、部品共用・設計標準化・機能拡張の柔軟性を実現し、お客様のニーズへの迅速なカスタマイズ対応を可能とする。

・施策② 基板小型化

基板の多層化や小型部品の採用による省スペース設計を推進する。これにより、筐体流用が可能となり、開発期間の大幅短縮を実現し、製品をより早く市場投入でき、お客様への迅速な製品提供を可能とする。

・施策③ 基板省電力化

低消費電力デバイスの採用や省電力モードの導入を推進する。これにより、全機種への環境負荷低減技術の展開が容易となり、お客様の運用コスト低減につなげる。

これらの施策により、個別最適設計からベースアーキテクチャーへの転換と技術基盤の強化を目指す(図2)。

ベースアーキテクチャーの構成

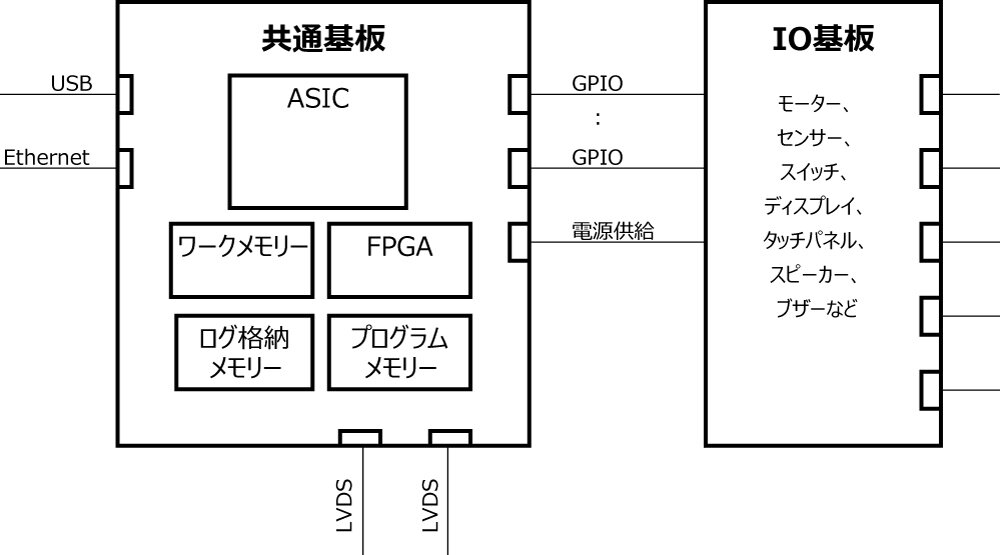

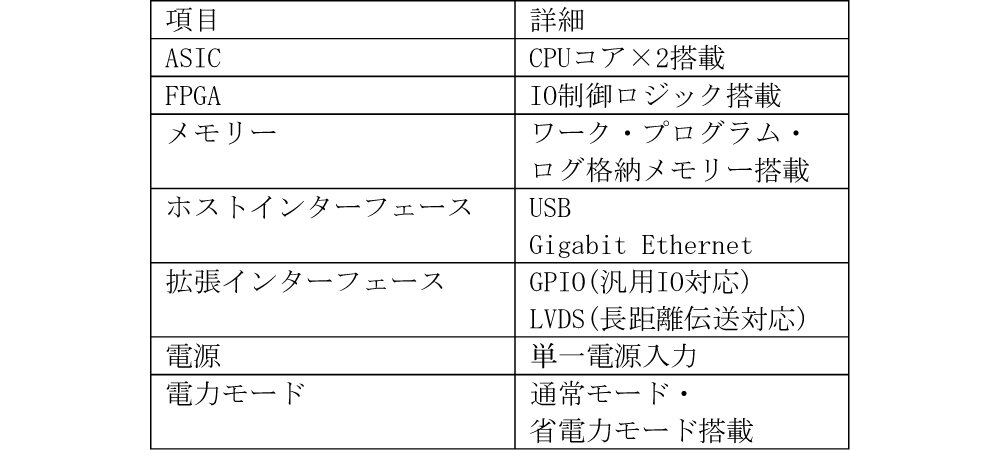

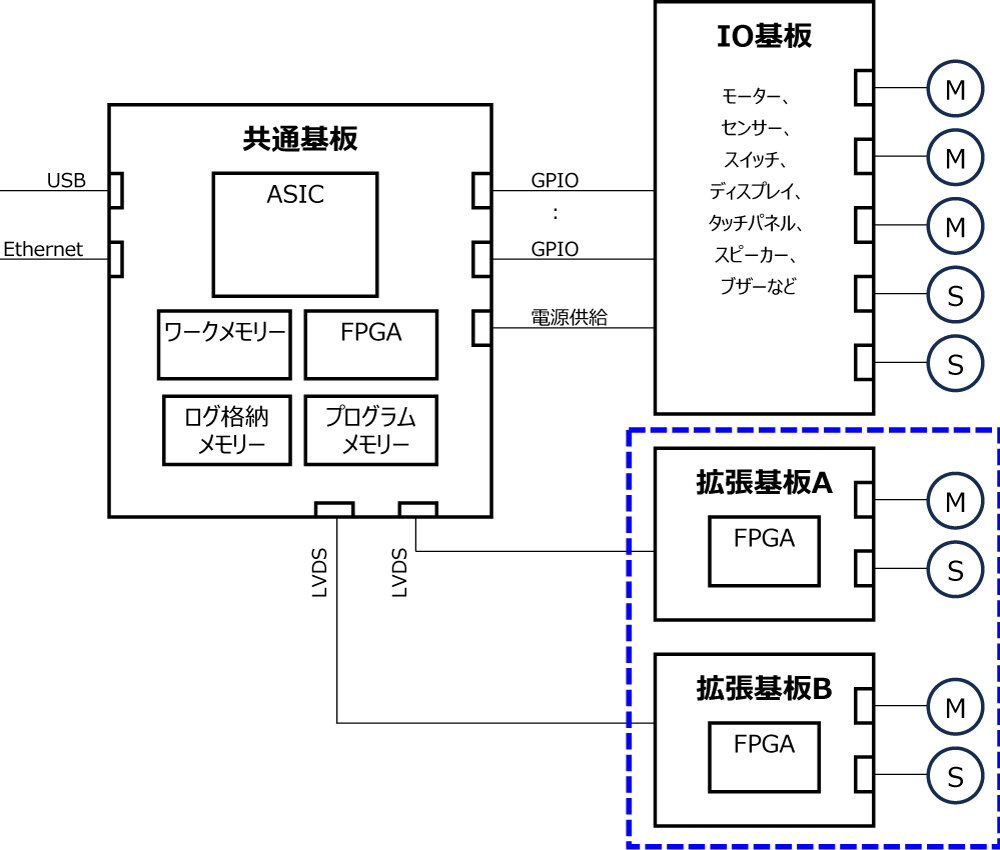

本章では、開発した共通基板の構成と代表的な仕様について説明する(図3)(表1)。

共通基板に搭載するCPUは、自社開発したASIC(Application Specific Integrated-Circuit)を採用する。加えて、柔軟な制御に対応するためFPGAを搭載し、各用途に応じたメモリーを搭載している。また、ホストインターフェースにはUSB® (注1)やGigabit Ethernet(注2)を搭載し、拡張性確保のため複数種類の拡張インターフェース(GPIO(注3)、LVDS(注4))を搭載した。

表1 共通基板の概略仕様

施策① 基板分離構成の実現例と成果

本節では、基板分離構成の具体的な設計実現例と成果について詳述する。

ベースアーキテクチャーの根幹として採用した基板分離構成は、主要機能を集約した共通基板と、各機種の固有機能を担うIO基板に分割する設計思想に基づく。この方針により、これまで個別最適化が積み重なっていた基板設計の共通化を推進した。

まず設計段階では、各機種で共通して利用される機能や要件(制御機能、通信機能、メモリー容量、インターフェース種類など)を洗い出し、共通基板に集約した。一方で、各機種の固有機能や要件(紙幣搬送制御、媒体有無監視制御、電源容量など)についてはIO基板に実装する設計とした。これにより、機能的な重複を排除しながら、個別要件に柔軟に対応できる構成とした。

基板分離による共通・固有の役割分担の例として、拡張インターフェースと電源回路の設計を挙げる。拡張インターフェースは、最大IO数を想定した多ピンGPIO対応とし、将来的な機能追加や装置仕様変更に柔軟に対応できるよう、FPGAなどのデバイス拡張を想定したLVDS通信を搭載した(図4)。この設計は、事業展開や市場ニーズの変化に合わせたベースアーキテクチャーの柔軟性と拡張性を高める狙いがある。電源回路は、各機種の機能規模や運用負荷に対応できるようにIO基板で容量を確保し、過不足なく安定した電力供給を実現している。共通領域と個別最適領域の役割分担を明確にすることで、信頼性やコスト、効率のバランスを最適化し、ベースアーキテクチャーの価値を発揮できる設計とした。

本設計の成果として、共通基板を各機種に適用しても性能低下がなく、部品共用と設計標準化、さらに機能拡張の柔軟性を達成した。これにより、従来製品と比べて開発期間の短縮と部品調達の安定化による供給リスクの低減が見込まれる。

施策② 小型化の実現例と成果

本節では、基板小型化の具体的な設計実現例と成果について詳述する。

前節で基板分離構成による効率的な機能配置や各機種の異なる要件への対応を紹介したが、一方で、接続部の増加により、共通基板とIO基板を含めた全体が大型化するというデメリットが生じた。これを克服するため、共通基板の小型化を重要な技術課題と捉え、設計手法と実装技術の大幅な見直しを行った。

まず、従来の4層基板構造から多層ビルドアップ基板へ切り替え、配線層数を増やすことで配線経路の自由度と集積度を大きく向上させた。これにより、従来よりも複雑かつ高機能な回路を、よりコンパクトに基板上へ集約することが可能となった。あわせて、部品レイアウトをゼロベースで見直し、配線パターンの最適化にも工夫を重ね、高密度で搭載できる構造を実現した。

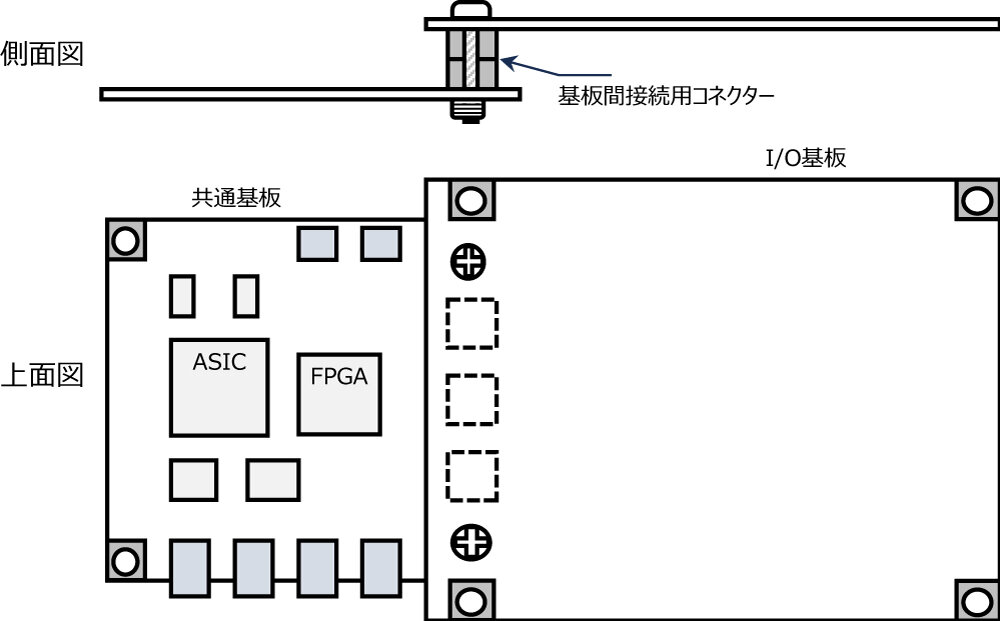

小型化を追求する過程では、面積だけでなく高さ方向の制約にも対応する必要があった。基板分離によって接続部が増加するなか、基板間接続用コネクタには小型・低背タイプを複数採用し、全体の厚みを抑えている。しかし、基板間接続用コネクタを複数同時に嵌合させる実績はこれまでなく、部品実装時のズレによる嵌合不良が課題として想定された。そのため、実装ズレの要因を事前に分析・検証し、問題ないことを確認するとともに、フットプリントやレイアウトを見直すことで、確実な嵌合性と高密度実装を両立している。

こうした取組みの結果、配線効率が大幅に向上したが、同時に多層化と高密度化により、高速信号伝送の品質維持という新たな技術課題も顕在化した。特に高速信号伝送では、近接配線からのノイズ干渉やクロストークが信号品質低下につながる懸念が生じた。これに対しては、信号用途ごとの役割を明確化し、信号パターンの両側にGNDパターンを配置、さらにパターン幅や配線間隔の最適化によるノイズ対策・信号品質の確保を図った。加えて、設計段階から品質確保を図るため、SI(Signal Integrity)シミュレーションを実施し、高速信号系に限らず共通基板内のすべての重要信号について事前検証を行った。また、基板分離で追加された接続部についても、リターンパスとなるGNDピンを信号ピンの両側に配置し、基板上のGNDと適切に接続することでノイズ耐性を強化している。

このような小型化と信号品質に配慮した多面的な設計により、分離構成の課題を克服しながら、性能や信頼性を損なうことなくコンパクトな基板設計を実現した(図5)。この結果、配線効率は従来比の2倍以上向上し、サイズは従来比の半分に抑えられた。これにより装置内スペースの有効活用やコスト削減が可能となり、さらに多機種展開や仕様変更にも柔軟に対応できるため、コンポーネントの競争力向上に貢献できた。

施策③ 省電力化の実現例と成果

本節では、基板省電力化の具体的な設計実現例と成果について詳述する。

前節で小型化への取組みを紹介したが、ベースアーキテクチャーをさらに強化するうえで、環境負荷の低減や運用コスト削減につながる省電力化も不可欠と考えた。省エネルギーや環境負荷低減への社会的要請が高まる中、エンタープライズソリューション事業製品においても装置全体の消費電力低減が求められている。本開発では、省電力化をベースアーキテクチャーの柱の一つに据え、ハードウェア・ソフトウェア両面で対策を講じた。

具体的には、共通基板に搭載したASICの機能を活用し、省電力モードの制御機能を実装した。また、主要機能を集約した共通基板と、各機種の固有機能を担うIO基板それぞれを電源制御できる設計を採用した。この構成により、運用ニーズに応じた柔軟な省電力制御が実現可能となった。

この設計では、用途に応じて2つの運用パターンを選択できる。復帰時間を優先する場合は、共通基板を常時通電したままIO基板のみを省電力モードに切り替えることで、主要機能は常時起動状態を維持したまま素早い復帰を可能としている。一方、省電力効果を最大化する場合は、共通基板とIO基板の両方を省電力モードに切り替えることで、IO基板だけでなく共通基板に搭載された多くのデバイスも非通電状態とし、復帰に最低限必要なASIC内部機能のみ通電状態としている。これにより消費電力を大幅に削減できるが、復帰時には主要機能の再立ち上げが必要となるため、所要時間はやや長くなる。こうした運用パターンを柔軟に切り替えられる設計とすることで、多様な現場や装置ごとに最適な運用選択を可能とした。

さらに、省電力モードの切り替えや復帰のタイミングは、共通基板に実装した管理ソフトウェアで装置の稼働状況や外部からの指示に合わせて自動制御している。これにより、無駄な消費電力が発生しないようにきめ細かく調整でき、待機時のエネルギー消費を最小限に抑えた。

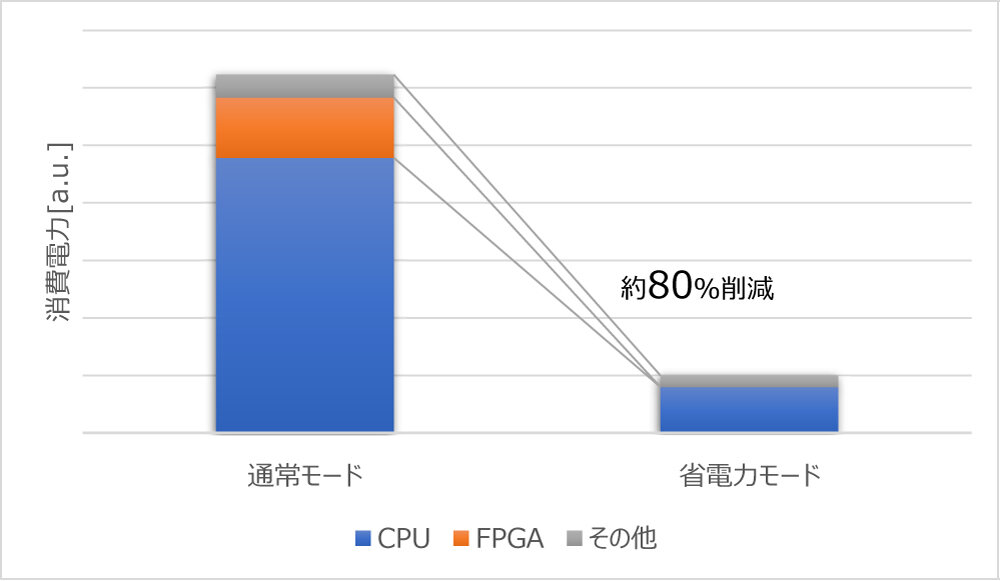

これらの多角的な省電力化への取組みにより、通常モード時に比べて最大80%の消費電力削減を行い、大幅な省電力化を実現した(図6)。また、復帰時間や省電力効果などを用途に応じて柔軟に選択できる技術基盤となった。こうした対応は、環境負荷の低減や顧客満足度の向上に加え、コンポーネントの競争力向上に貢献する成果となった。

今後の展開

本稿では、個別最適設計からベースアーキテクチャーへの転換、および技術基盤の強化を目的とし、基板分離構成による部品共用と設計標準化、基板の小型化と高密度化、省電力モードをはじめとする環境負荷低減技術など、三つの施策を軸に具体的な設計実現例とその成果を紹介した。

今後は、これらをエンタープライズソリューション事業のみならず他事業分野にも展開し、全社的な技術基盤の拡充やAI処理技術などの新機能開発にも柔軟に対応することで、OKIグループ全体の価値創出と事業発展に貢献していく。

参考文献

(参考文献1)OKI IR Day(2023年11月16日開催)、技術戦略説明資料 [4.0MB]

(参考文献2)齋木祥廣、渡辺啓介、若林円:エンタープライズソリューション事業製品の次世代プラットフォーム技術、OKIテクニカルレビュー第242号、Vol.90 No.2、pp40-43、2024年2月

(参考文献3)宮村紀秀:低消費電力・小型化を特長とするOKI ASICを活用したAIシステム、OKIテクニカルレビュー第243号、Vol.91 No.1、pp76-79、2024年12月

筆者紹介

金井拓也:Takuya Kanai. 技術本部 研究開発センター ハードウェア研究開発部

用語解説

- IO(Input/Output)

- 入出力信号やデータのやり取りを行うインターフェース。

- 多層ビルドアップ基板

- 高密度実装向けに開発されたビルドアップ工程を取り入れたプリント基板。

- (注1)USB(Universal Serial Bus)は、USB Implementers Forumの登録商標です。

- (注2)Gigabit Ethernetは、IEEEによって標準化されたEthernet規格です。

- (注3)GPIOは「General Purpose Input/Output」の略です。

- (注4)LVDSは「Low Voltage Differential Signaling」の略です。