# 超高多層基板の開発

新保 靖行

沖プリンテッドサーキット株式会社では、通信分野で培われた多層化、特性インピーダンス制御技術を元に、他の市場における高多層基板への展開を図ってきた。特に、半導体テスタ基板においては、50層クラスの量産に対応するに至った。

しかし、昨今、メモリの増加に伴うテスタ基板の配線 収容の要求が増加する一方、テスタ装置に組み込むという基板サイズ(板厚)の制限下で対応することが求められている。このような要求に対して、従来の基板構造で対応するには、60層以上の層数が必要となり、既存の製造技術では対応できないのが実状である。40層を超える層数の場合、一般的なプリント基板の製造方法では対応が難しいため、多配線を収容できる超高多層基板の開発が急務であった。

本稿では、半導体テスタ基板市場の要求へ応えるべく「メモリ増加に対応した半導体テスタ基板」としての80層超高多層基板の実現に向けた技術開発について紹介する。これを実現するためには、①製造技術の開発、②基板材料の開発、③設計手法の開発、という視点からのアプローチで解決することができた。また、これらの開発技術は、半導体テスタ基板だけではなく、更なる高速、高密度化が進む通信市場向け基板への展開が図られる。

# 超高多層基板開発の必要性

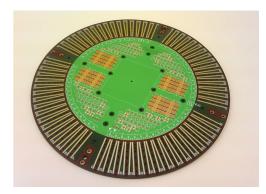

プリント基板とは、一般的に電子部品を実装し、電子 回路を形成するための部品である。このプリント基板構造を利用した特殊用途として、半導体テスタ基板が半導体製造過程でのテスタ治具として使用されている。特に、本稿で紹介するプローブカード(写真1)は、製造途中のウェハ上に回路が形成された段階でテスト(ウェハテスト)を行う治具である。プローブカードの場合、基板表面には、電子部品ではなくプローブと呼ばれる針が実装されている。近年、プローブカードは、ウェハ径の拡大とチップの微小化に伴い、テスト回路が増大し、プローブカードへの高密度配線収容の要求が高まっている。特に、メモリ向けテスタでは、この傾向が顕著である。

プリント基板の全般的な市場規模に対して、半導体テ

スタ基板の市場は決して大きくはない。しかし、本稿で紹介する超高多層基板開発の各要素技術は、プリント基板の基幹となる技術であり、本技術を深耕することで、半導体テスタ基板だけではなく、他の商品(基板)にも展開が可能となる。すなわち、

1.他の商品への技術展開による市場拡大 2.技術的優位性 が期待できる。

写真1 プローブカード

# 超高多層基板における製造技術開発

一般的なプリント基板が板厚1.6mmで12層程度までなのに対して、開発目標の超高多層基板では板厚6.3mmで80層になることから、以下に示すような製造技術課題を解決する必要があった。

#### (1) 積層技術

各層を積み重ねる時の層ずれ抑制技術が必要となる。層ずれ抑制技術として、積層時の位置合わせに用いる基準穴の穴明け工程を見直した。さらに、積層時のクッション材を見直すことにより、最大層ずれ量150μm以上を60μm以内に抑制することができた。そして、貫通穴と内層隣接配線とのショートが回避できるようになった。

# (2) 穴明け技術

高多層基板の場合、高精度な穴位置、穴断面形状、高

アスペクト比の穴明け技術が必要となる。厚板に小径ドリルで穴明けする場合、ドリルが曲がることにより、穴位置のずれやドリル折れが発生する。これを抑制するために、ドリル刃長の異なる複数本を使用する穴明け方法や、基板両面から穴明けする方法などの技術開発を行った。この結果、穴位置精度±100μm以上だったものが±60μm以内に向上して、貫通穴と内層隣接配線とのショートが回避できるようになった。

#### (3) メッキ技術

板厚の増大、穴径の微小化に伴い、高アスペクト比のメッキ技術が必要となる。弊社では、新規電気メッキ装置の導入に際して、槽内電流分布をシミュレーションし、メッキ装置を開発した。さらに、新しいメッキ液の導入やメッキ条件の最適化により、アスペクト比30に対応した。これにより、板厚6.3mm穴径 φ0.20mm(アスペクト比約32)において、電解メッキとしては業界トップレベルのスローイングパワー(穴内メッキ厚/表面メッキ厚の比)50%以上を達成できた。

#### (4) 特性インピーダンス制御技術

高速、低損失の伝送を行うためには、特性インピーダンス制御技術が必要となる。製造技術で制御できる主な因子として、①配線幅、②絶縁層間厚、が挙げられ、それぞれ高精度に制御する必要がある。①配線幅に関しては、配線(パターン)形成の製造装置性能によるところが大きいが、②絶縁層間厚の制御は各種基板材料を使用することから、厚みのばらつきを制御すると同時に、各材料での仕上がり厚予想値をシミュレートし、その結果を元に設定配線幅にフィードバックをかけて目標値になるようにしている。弊社では、このために各種基板材料を元に積層後の絶縁層間厚、比誘電率などをデータベース化した自社開発のシミュレータを構築し、より高精度な特性インピーダンス制御を実現することができた」。

弊社では、これらの製造技術を組み合わせることで、板厚4.8mmで $\phi$ 0.2mmドリルを使用して0.5mmピッチBGAに対応、板厚6.3mmで $\phi$ 0.25mmドリルを使用して0.65mmピッチBGAに対応、さらに板厚6.3mmで50層クラスの量産化を実現している(**写真2**)。

しかし、これらの製造技術を組み合わせても、従来技術の延長線上では、一般的に入手できる基板材料、設計仕様のために限界が見えてくる。プローブカードの場合には、板厚6.3mm、基板サイズ \$480mmという大きさの制約に加え、配線の直流導体抵抗値の制約、特性インピー

ダンス制御の制約から、実現できる層数は50層程度が限界となる。目標とする80層の超高多層基板を実現するためには、以上のような製造技術的視点からは不十分であり、より高多層化できる極薄基板材料の開発、配線収容性を高めた層数低減設計手法の開発、という新しい視点からのアプローチが必要となった。

写真2 板厚4.8mm0.5mmピッチ 板厚6.3mm58層

#### 超高多層基板実現のための基板材料開発

更なる高多層化を実現するためには、極薄基板材料を使用することになるが、絶縁層間厚が薄くなることにより、特性インピーダンス配線幅が細くなってしまう。配線幅が細くなると、直流導体抵抗が高くなり、減衰(ロス)も大きくなる、という弊害が発生する。

この弊害を解決するためには、低誘電率材の採用が有効である。プリント基板の材料は、FR-4呼ばれるガラスクロスとエポキシ樹脂の複合材が一般的であるが、FR-4の比誘電率は4.7~3.8程度である。これらの材料と、一般的な銅箔厚 $35\,\mu$ mで、直流導体抵抗と特性インピーダンスを整合するためには、線幅 $100\,\mu$ mで層間厚 $100\,\mu$ m程度が必要となる。一部、比誘電率が3.0以下の材料(PPE樹脂やPTFE樹脂等)も存在するが、材料コストが高く、加工性が劣ることから、実現性が低い。たとえばFR-4系材料で比誘電率3.5以下まで下げる改良が実現できれば、配線幅を確保しつつ、層間厚を薄くすることができる。

そこで、低コストで既存の加工プロセスが流用できる 事をコンセプトに、FR-4をベースとした基板材料の低誘 電率化を検討した。

従来のFR-4材は、比誘電率3.5程度のエポキシ樹脂と

6.0程度のEガラスと呼ばれるガラスクロスの複合材となっている。そのため、材料としての比誘電率は、4.7~3.8程度が限界であった。材料としての比誘電率を下げるためには、ガラスクロスの比誘電率を下げることが必要となる。そこで、まだ一般的ではない低誘電率ガラスクロスの採用、および樹脂とガラスクロスの比率を変更することで、開発を進めている。

この低誘電率材を採用することにより、層間厚100μm 以下でも、直流導体抵抗および特性インピーダンス制御 を満足できるようになった。

# 超高多層基板実現のための設計手法開発

極薄基板材料を採用しても、配線幅の制約や製造装置の制約による限界がある。そのため、別の視点から、層数増加を抑制または削減する手法として、設計手法からの解決を試みた。

プリント基板では、構造上、同一層内で配線を交差することができない。配線を交差する必要がある場合には、 貫通穴を介して、他の層へ配線する必要がある。配線を うまく交差できる設計手法が開発できれば、層数増加の 抑制が図られる。

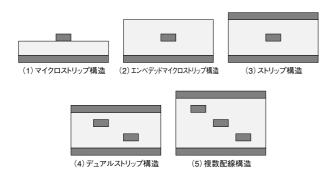

また、特性インピーダンス制御をする上で、配線層に対して、リファレンス層となるGND層が、上下に1層ずつ必要となる。一般的なストリップ構造で配線層を増やした場合、配線層とGND層は1対1で、配線層と同数のGND層が必要となり、全体の層数に対して、配線層だけを有効的に増やすことができない。配線層だけを有効的に増やせる設計手法が開発できれば、相対的にGND層が削減できる。

#### (1) 層数増加の抑制(交差配線の実現)

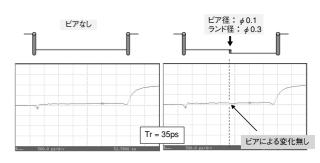

単純なストリップ構造では、GND層に挟まれる配線層は1層のみのため、構造的に交差配線することはできない。しかし、デュアルストリップ構造を取り入れることで、配線層が2層となり、配線層間をビアで接続することにより、立体交差が可能となる(図1)。ただし、ビアを含む伝送線路の特性インピーダンス制御や伝送特性の確保が課題となる。

そこで、弊社では、ビア径およびランド径の大きさによる、特性インピーダンスと伝送特性の変化を確認して、設計仕様の最適化を行った。その結果、穴径0.1mmでランド径0.3mm以下の場合について、特性インピーダンス変化を実測した結果3%以内に収まることが確認できた(図2)<sup>21</sup>。

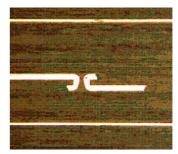

このような微小径のビア加工は、弊社が導入している

図1 デュアルストリップ構造による交差配線模式図

図2 微小ビアによる特性インピーダンス変化 (時間領域反射法 (TDR) による実測)

写真3 レーザ加工微小径ビア

UV-YAGレーザ加工機により実現できた(写真3)。

# (2) 層数の削減(複数配線構造の可能性)

弊社では、現在マイクロストリップ構造、ストリップ 構造だけではなく、デュアルストリップ構造の特性イン ピーダンス制御に対応している(図3)。この場合、クロ ストークの影響を少なくするための設計手法が必要となる。

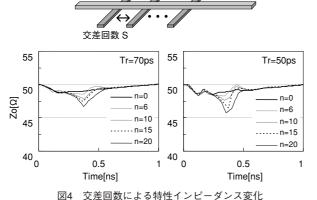

超高多層基板を開発する上で、その層数を有効に活用するためには、基板全体の層数に対してリファレンス層の比率を下げ、配線層の比率をいかに上げられるかが鍵となる。これを実現するために、弊社ではリファレンス層間に配線層を3層組み込んだ構造の実現化を進めている。同時にこの構造は、隣接信号との影響による特性インピーダンス変化、クロストークなどの特性の確保が非常に難

図3 特性インピーダンス制御基板の構造

交差回数 n

信号層配線

(シミュレーションによるTDR応答)

しくなるという課題があるが、電気特性を確保するための設計条件の確立を、シミュレーションおよび実測から行っている(図4) $^3$ 。

このような複数配線構造を確立することにより、配線層の相対的な増加が見込まれる。また、各層間を薄くしても、3層の配線層の内、中心の配線層はリファレンスとなるGND層との間隔が稼げるため、特性インピーダンスの低下が防げ、線幅を太く確保することができる。

これらの相乗効果により、通常のストリップ構造と比較して、信号層数の増加が見込まれる。

2009年のJPCAショーでは、複数配線構造を採用した 80層板の試作基板を参考出展した(写真4)。

今後は、複数配線構造の設計手法の確立を目指し、商 品化を進める予定である。

# あとがき

本稿で紹介した、各要素技術を複合することにより、 80層超高多層基板実現の可能性が見えてきた。これらの 技術は、半導体テスタ基板だけではなく、その他の商品

写真4 80層基板断面写真

にも展開することで、市場拡大を目指している。また、これらの技術確立による技術的優位性を狙い、受注型の営業形態から、基板構造の提案、各種シミュレーションの実施、設計、製造、実装までの提案型営業形態(トータルボードソリューション)への転換を目指している。

# 参考文献

- 1) 金田勲 他: インピーダンスコントロール基板, 電子材料, 2001年10月号, pp.96-100, 2001年

- 2) 八木貴弘 他:高速高密度多層プリント配線板における層数抑制手法,第22回エレクトロニクス実装学会講演大会,17A-06,2008年

- 3) 上谷純 他: 超高多層プリント配線板の信号収容性に関する一考察, 第23回エレクトロニクス実装学会講演大会, 12B-05, 2009年

# ●筆者紹介

新保靖行:Yasuyuki Shinbo, 沖プリンテッドサーキット株式会社 技術本部 商品開発部 試作開発チーム