# 携帯機器向け 超低電圧動作の強誘電体メモリ

佐久間 信三 林 孝尚

PDA、携帯電話をはじめとする携帯機器へ不揮発性メモリをプログラムやデータ格納用メモリとして搭載することが一般的になってきている。例えば、インターネット上からダウンロードしたアプリケーションをこれらの不揮発性メモリへ格納することにより、携帯機器の機能拡張が可能となる。しかし、従来不揮発性メモリとして主に使用されるフラッシュメモリ、EEPROM等は書き換え回数が少ない、書き込み時間が長い、書き込み電圧が高く消費電力が大きい。バッテリー駆動である携帯機器は、特に低消費電力が要求されており、課題となっていた。強誘電体メモリは、10<sup>10</sup>回以上の書き換えが可能、書き込み時間が短く読み出しと同じ時間で可能、書き込みに高電圧を必要としないため消費電力が小さいなど、携帯機器への搭載に適している。

今回, 低電圧動作に有利な強誘電体材料を採用し, 1.8V で動作する強誘電体メモリを開発した。

## 強誘電体メモリ技術

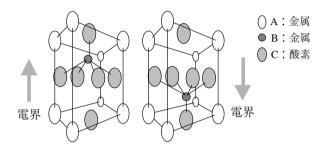

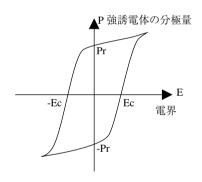

強誘電体メモリはPZT (PbZrxTi₁-xO₃) やSBT (SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>) などの強誘電体材料の持つ分極特性をメモ リに応用したものである。これらの強誘電体材料は、ペ ロブスカイト構造と呼ばれる結晶構造をとる。強誘電体 は、膜の両端に一定レベルの電位をかけることにより結晶 格子の原子が電界の向きに移動し分極状態となる(図1)。 この分極状態は膜の両端の電位を取り去った後も維持さ れる。分極量(P)と膜への印加電界(E)の関係は、図 2のようなヒステリシスを持ったP-E曲線となる。再び膜 の両端に電位をかけることにより分極状態を読み出すこ とができる。PZTは膜の両端への電位を取り去った後の 分極量, 残留分極量 (Pr) が大きいという特徴があるが, 書き換え電圧のめやすとなる抗電界(Ec)は高い。一方 SBTは、残留分極量はPZTと比較して小さいが抗電界は 低い。つまり、電源電圧が或るレベル以上であれば、残 留分極量が大きいPZTが有利であり、低電圧で動作させ るためにはSBTの方が有利となる。携帯機器向けとして、 低電圧動作に有利なSBTを採用した。

図1 強誘電体の結晶構造(ペロブスカイトABO。構造)

図2 P-Eヒステリシス曲線

# 低消費電力設計

低消費電力を達成するため、動作電源電位の低電圧化、 動作時電流低減、待機時電流低減を行った。

#### (1) 動作電圧の低電圧化

SBT強誘電体キャパシタ特性を最大限活用するため、動作速度に制限があるものの、周辺回路を1.5Vまで動作可能なように設計した。このため2V系電源の最低動作保証電位である1.8Vに対し十分な余裕を持たせることができた。併せて3V、2.5V系の電源にも用いることができるよう最大動作電圧は3.3Vまで動作するように設計した。

#### (2) 動作時電流の低減

一度に動作するビット数を32ビットとすることにより、動作時のセンス電流を低減した。一度に動作するビット数を減少させれば、センス電流を更に低減することも可能であるが、センス制御回路数増加がチップ面積を増大させる。総メモリ容量64kビットでの最適値として32ビットを同時活性することとした。

#### (3) 待機時電流の低減

待機時は強誘電体メモリマクロ内のすべての動作を停止させた。メモリアクセス時に必要な昇圧電位(ワード線電位)発生回路についても、アクセス命令が入力されてから昇圧を開始し、アクセス終了後に再び動作を停止させるようにしたため、待機時にはトランジスタのリーク以外の電流は全く流さないようにした。

以上の低消費電力設計により、従来の不揮発性メモリ に較べて、低電圧動作が可能となった。

# 強誘電体メモリマクロ

混載においてはメモリ容量,データバス幅の要求が多種となる。今回強誘電体メモリマクロの開発では,要求仕様に合わせメモリ容量が容易に変更可能なように,8kビットを最小単位とし最大8個まで接続可能にした。したがって,8kビット刻みで最大64kビットまで対応することができる。また,入出力回路部では8ビット,16ビットの2種類のデータバス幅に対応可能とした。

表1に強誘電体メモリマクロの主要諸元を示す。

表1 強誘電体メモリマクロ主要諸元

| 項目      | 諸元               |

|---------|------------------|

| セル方式    | 2T2C             |

| メモリ容量   | 8kビット-64kビット     |

|         | (8kビット刻み)        |

| データバス幅  | 8ビット、16ビット       |

| 電源電圧    | 2.0V±0.20V       |

|         | $2.5V \pm 0.25V$ |

|         | $3.0V \pm 0.30V$ |

| データ保持時間 | 10年              |

| アクセス回数  | 1010回            |

#### プロセス開発

低電圧動作を実現させるためSBT膜の薄膜化を進めた。 膜厚120nmで良好なリーク電流特性を保持しつつ、デバイス動作に十分な大きさの残留分極値を実現するSBT成 膜プロセスを開発した。また強誘電体メモリの下地CMOS部分およびメタル配線層は、 $0.5\,\mu$ m Nwell CMOSプロセスをベースに構築した。

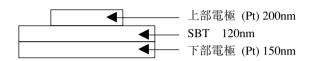

### (1) 強誘電体成膜プロセスおよび電極構造

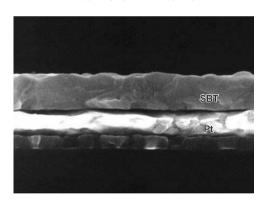

強誘電体材料であるSBT原料溶液はゾル・ゲル法で作製した。SBT原料溶液をスピンコート法により下部電極上に塗布・焼成し、強誘電体薄膜の成膜を行った。電極材料は上部電極および下部電極共に白金(Pt)を用いた。図3に断面構造の模式図を示す。

図3 強誘電体キャパシタの断面構造

#### (2) 強誘電体膜の薄膜化

SBT膜が完全に分極反転するのに必要な電界はSBTの 抗電界(Ec)によって決まり、約3Ec程度とされている。 SBT膜のEcは45kV/cmであることから、3Ec=135kV/cm となる。1.8V以下の低電圧動作を実現するためには、

1.8 (V) /[135×10<sup>3</sup> (V/cm)] =

$$1.33 \times 10^{-5}$$

(cm)

= 133 (nm)

すなわち強誘電体膜厚を約130nm以下にしなければならないことになる。

一般に強誘電体膜を薄膜化すると、電極界面の分極反転に寄与しない遷移層の割合が相対的に増大するため、分極電荷量(Pr)が低下する。また大きな問題として130nm以下にSBTを薄膜化すると、SBTの粒径のバラツキ(SBT表面の凹凸)に起因する電気的耐圧(上部電極と下部電極がショートする電圧)が大幅に低下するといった問題が発生する。

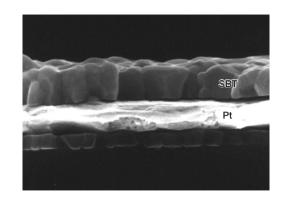

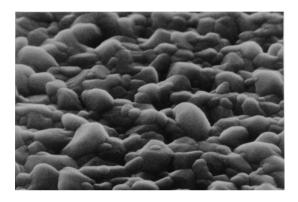

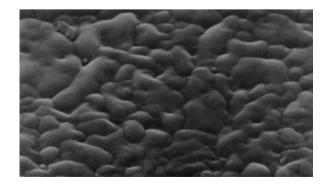

今回これらの問題を解決するため、SBTの溶液組成の見直しと焼成条件の最適化を実施した。図4(a)には従来のSBTの断面SEM写真を、図4(b)には表面SEM写真を示す。一見して明らかなように、SBTの表面形状は非常に悪い。このため局所的にSBT膜厚の極端に薄い部分が存在し、結果として電気的耐圧の低下をもたらしてしまう。そこで、SBT溶液のBi添加量を最適化し、現在図4(c)および図4(d)に示すように良好な平坦性を持つ強誘電体薄膜を得た。結果、現在100nm程度への薄膜化は十分に可能なレベルに達している。

図4(a) 従来のSBTの断面写真

図4(b) 従来のSBTの平面写真

図4(c) 開発したSBTの断面写真

図4(d) 開発したSBTの平面写真

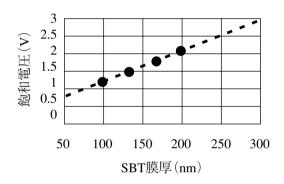

#### (3) 強誘電体特性

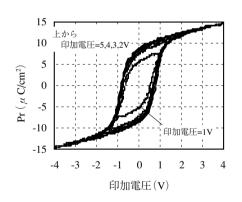

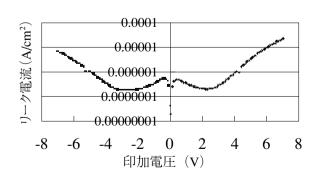

図5にSBT膜厚と残留分極値の飽和電圧との関係を示す。ここでSBT膜が完全に分極反転する印加電圧を印加したときのPr値の90%に達する電圧を飽和電圧と定義した。膜厚170nmにおいて1.8Vの飽和電圧が得られている。図6には膜厚120nmにおけるP-Eヒステリシス特性を,図7にリーク電流特性を示す。120nmまで薄膜化したSBT膜でも良好な強誘電特性を示し,またリーク電流に関しても極めて良好であることがわかる。以上より,1.5-1.8Vの低電圧においても,強誘電体メモリの動作が可能であると言える。

図5 SBTと飽和電圧値

図6 SBTキャパシタのヒステリシス特性

図7 強誘電体キャパシタのリーク電流特性

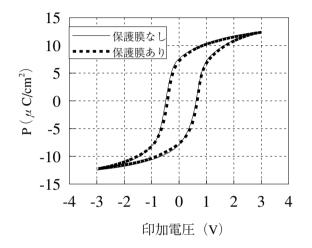

#### (4) プロセスダメージの低減

強誘電体膜(SBTおよびPZT)は酸化物結晶であるため、電極加工時のダメージや、その後の配線、酸化膜形成、保護膜形成プロセスから発生する還元雰囲気による還元作用により、残留分極特性等の強誘電体特性やリーク特性が大きく劣化する。これらを抑制するため電極形成後の配線・層間膜形成時の還元雰囲気の低減および、バリヤ膜の導入により強誘電体特性の劣化を防いでいる。図8に示すように保護膜形成前後でほとんど劣化の無い特性が得られている。

図8 保護膜形成前後のヒステリシス特性

#### (5) 信頼性特性

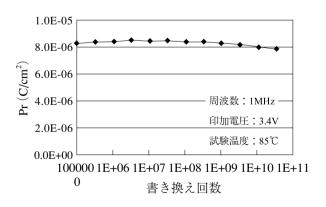

図9にファティーグ(繰り返し書き込み耐性)特性を示す。10<sup>10</sup>回を超えても劣化のない結果が得られている。

図9 ファティーグ特性

# 強誘電体メモリマクロ評価

試作評価のため0.5 μ m強誘電体キャパシタ混載プロセ

スを用い、メモリ容量64kビット、データバス幅8ビット/16ビットの強誘電体メモリマクロのテストチップを試作した(図10)。評価の結果、電源電圧1.8V~3.3Vの範囲で動作することを確認した。

図10 64kビット強誘電体メモリチップ写真

# あとがき

SBTの薄膜化およびプロセスダメージ低減により、不揮発性メモリとしては超低電圧である1.8Vで動作可能な強誘電体キャパシタプロセスを開発した。超低電圧での読み出し、書き込み動作可能であり、待機時、動作時消費電流の小さい、携帯機器に適した不揮発性メモリとして、0.5μm混載用強誘電体メモリマクロを開発した。

2V系電源のみではなく、単一チップにて2.5V、3V系電源にも対応したことにより、同一チップ上のロジック回路と同一電源で不揮発性メモリを動作させることができる。

今後, 更に低消費電力化を行い, 携帯機器に最適な不揮発性メモリとして強誘電体メモリの開発を継続する予定である。 ◆◆

#### ●筆者紹介

佐久間信三: Shinzo Sakuma.シリコンソリューションカンパニー LSI事業部 IP開発部

林孝尚:Takahisa Hayashi .シリコンソリューションカンパニー 超LSI研究センタ 低エネルギーデバイス研究部