# 次世代AI半導体の検査装置用 124層PCB技術開発

中條 嶋太 新保 靖行

OKIサーキットテクノロジー株式会社(以下、OTC)上越事業所では、高多層・高精細・大型プリント配線板(以下、PCB)に関する高い開発・生産技術力と実績を保有している。上越事業所において、AI半導体に搭載されるHBMなど次世代広帯域メモリー向けウエハ検査装置用である124層PCB技術の開発に成功した(写真1)。本稿では124層PCB技術の開発成功に至る製造技術と設計技術について述べる。

写真1 124層PCB

## 124層PCB技術の製造技術

AI処理は、GPU(画像処理半導体)とメモリー間で膨大なデータの伝送が要求されるため、GPUの性能が向上するほど、搭載されるメモリーには高速・高周波・高密度でのデータ転送能力が必要となる。HBMはDRAMを積層する構造であり、高い精度でウエハを薄く加工するため、検査装置用PCBにも従来以上に高い性能と品質が求められる。

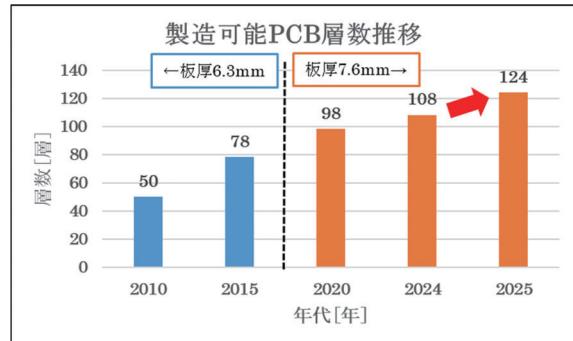

最新の半導体は信号数が膨大であり、プロセス微細化によりウエハ一搭載チップ数も増加する。そのため、半導体製造プロセスにおける検査装置用PCBは高密度化とともに積層数を増やす必要がある。一方で、さまざまな制約から板厚は7.6mmに抑える必要があり、従来技術では最大で108層が製造限界であった(図1)。

図1 OTC製造可能PCB層数推移

従来技術の限界であった108層を約15%上回る124層PCB技術を開発するため、「極薄材料の開発と適用」と「極薄材料に対応した製造プロセスの構築」を実施した。下記に詳細を述べる。また、開発した124層PCB技術の対応可能スペックも記載する。

### ●極薄材料の開発と適用

従来技術の限界であった108層を超えるさらなる高多層化を実現するためには、従来使用していたCCL(銅張積層板)及びプリプレグよりも更に薄い極薄材料の採用が不可欠であった。この課題に対し、材料メーカーと連携して、基礎評価及び高多層PCBの試作評価を繰り返し実施し、安定した品質での製造に向けた各種改良を行い、極薄材料の開発と適用を実現した。

### ●極薄材料に対応した製造プロセスの構築

極薄材料の適用にあたり、対応した製造プロセスの構築も不可欠であった。下記(1)～(3)に示す設備導入や治工具開発、製造プロセス改良を実施した。

#### (1) 極薄材料の自動搬送に対応した設備導入

極薄材料の取り扱いは、材料の極薄化に伴い、より高い精度と安定性を備えたハンドリング技術が求められる。この課題に対応するため、極薄材料の自動搬送に対応した最新の水平製造ライン設備を導入し、装置メーカーと共同

で、投入・受取りなどの自動化設備における極薄材料対応付加機能を開発した。加えて、材料厚みに応じた各製造ラインの処理条件最適化も実施した。これらにより、極薄材料を用いたPCB製造を実現した。なお、本設備導入は、OTC独自の条件チューニング・付加機能の共同開発によるものである。

### (2) 極薄材料専用の治工具開発

(1)によって、極薄材料を用いたPCB製造を実現したが、水平製造ラインにおいて高い品質を維持するために、さらなる対策が必要であった。この課題に対応するため、極薄材料専用の治工具を新たに開発し、安定した品質での製造が可能になり、生産性の向上にも貢献した。

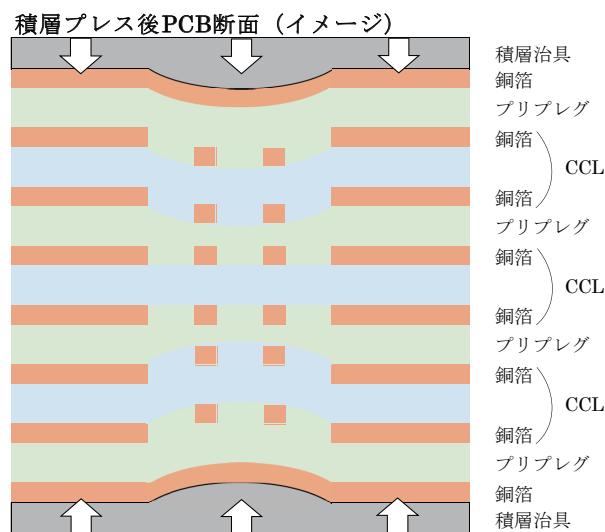

### (3) 積層技術の製造プロセス改良

極薄材料を用いた超高多層PCBの製造においては、各層を積み重ねる際の位置ずれを最小限に抑えるため、より高精度な積層技術が必要である。しかし、紙よりも薄く強度の弱い極薄材料でそれを実現するのは極めて難しいという課題があった。また、層数が増えることで使用するプリプレグの枚数も多くなり、PCB面内の板厚ばらつきが大きくなる課題もあった。これらの課題に対応するため、PCB上下の積層固定治具精度向上と積層合わせピン最適化によるCCL層間位置合わせ精度改善、PCB上下の積層固定治具配置見直し、積層時のクッション材最適化、積層条件(温度、圧力)の見直しなどの対策を実施した。これらの対策により、従来の高多層PCBと同等の面内板厚ばらつきに抑えるとともに、積層位置ずれ70μm以下を確保することができ、安定製造が可能となった。

### ●124層PCB技術対応可能スペック

124層PCBにおいても、108層PCBと同様に、穴ピッチ0.5mmまでの狭ピッチ設計に対応可能である(表1)。以下に、124層PCB・穴ピッチ0.5mmの断面写真を示す(写真2)。今後は、さらなる狭ピッチ化への対応に向けた技術開発を継続していく。

表1 PCB技術対応可能スペック表

|        | 108層PCB      | 124層PCB |

|--------|--------------|---------|

| 板厚     | 7.6mm        | 7.6mm   |

| 穴ピッチ   | 0.5mm        | 0.5mm   |

| 最小ドリル径 | 0.2mm        | 0.2mm   |

| 内層銅箔厚  | 1/2oz or 1oz | 1/2oz   |

写真2 124層PCB断面(板厚7.6mm 0.5mmピッチ)

### 124層PCB技術の設計技術

設計面での配慮事項として、極薄材料を用いた超高多層PCBを安定した品質で製造するためには、製造技術だけでなく、設計面での配慮も極めて重要となる。下記(1)～(4)に、その一例を述べる。

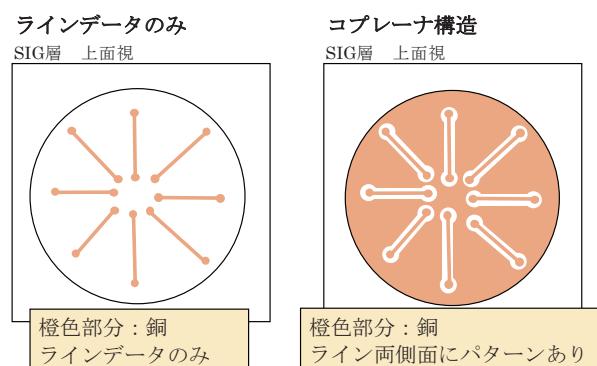

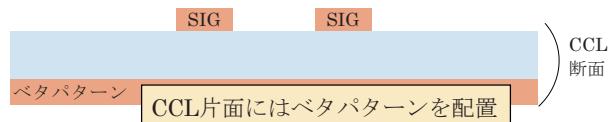

#### (1) SIG層(信号層)の設計

CCLの基材破損防止のため、CCL表裏ともに残銅率が低いSIG層/SIG層の構造は原則不可とすること。また、積層ボイド発生リスク低減のため、SIG層はラインデータのみとするか、コプレーナ構造が必要な場合は、CCL全面で残銅率が均一になるように設計すること(図2)。

図2 SIG層ラインデータのみ・コプレーナ構造(イメージ)

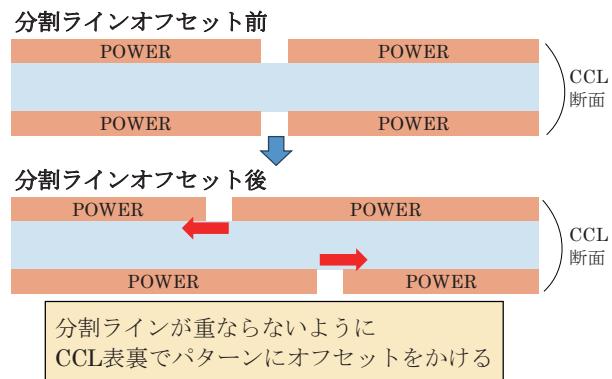

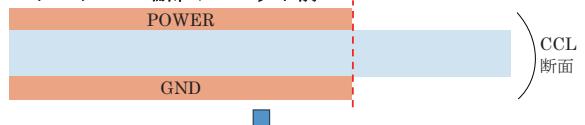

## (2) POWER層(電源層)の設計

CCLの基材破損防止のため、電源分割ラインの入れ方に注意すること。

### ①CCLの表裏がPOWER層/POWER層の場合

分割ラインがCCLの表裏で重ならないように、オフセットをかけること(図3)。

図3 POWER層分割ラインオフセット (イメージ)

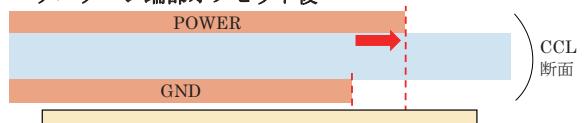

### ②CCLの表裏がPOWER層/SIG層の場合

分割ラインの配置によっては、CCLの強度が大きく低下するため、表裏の残銅率やパターンに配慮すること。

## (3) GND層(接地層)の設計

CCL面内でエリアごとの残銅率に大きな差があると、その差が各層で累積されることで、PCB全体の板厚ばらつきにつながる(図4)。

図4 CCL残銅率差によるPCB面内板厚差 (イメージ)

板厚ばらつきを抑え、平坦性を確保するためには、ベタパターンなどが特定のエリアに局所的に集中しないよう、配置に配慮すること。また、大面積のベタパターンについては、周囲と残銅率が均一になるよう、工夫を施すこと。(※SIG層、POWER層においても同様に、極力、CCL面内で残銅率が均一になるように配慮が必要である。)

## (4) 共通事項

CCLの基材破損防止のため、SIG層、POWER層、GND層共通して、ベタパターンの入れ方に注意すること。

- ①CCL片面にはベタパターンを配置すること(図5)。

- ②ベタパターン端部などは表裏でオフセットをかけること(図6)。

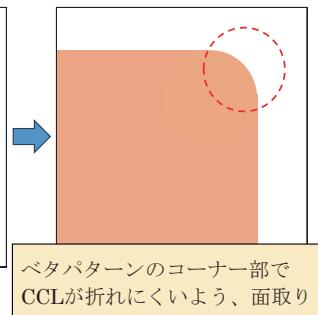

- ③ベタパターンのコーナー部は面取りすること(図7)。

図5 CCL片面ベタパターン配置 (イメージ)

### ベタパターン端部オフセット前

### ベタパターン端部オフセット後

図6 ベタパターン端部などオフセット (イメージ)

### ベタパターン

#### コーナー部面取り前

CCL 上面視

### ベタパターン

#### コーナー部面取り後

CCL 上面視

図7 ベタパターンコーナー部面取り (イメージ)

## あとがき

OKIサーフィットテクノロジー株式会社は、AI半導体、航空宇宙、防衛、ロボット、次世代通信など、将来の成長が期待される先端分野のPCB技術開発に注力している。これらの分野では、PCBの多層化・高密度化・大型化や高速・大容量通信への対応など、高度かつさまざまな技術が要求される。また、信頼性・安全性の確保も求められる。今後も、業界のトレンドや顧客の要望を的確に捉え、さらなる高度な技術開発へと挑戦し続けることで、社会の発展に貢献していく。

なお、124層PCB技術の開発については、沖電気工業株式会社が2025年4月に発表したプレスリリースでも紹介している<sup>1)</sup>。

## ■参考文献

- 1) OKIプレスリリース、次世代AI半導体の検査装置用124層PCB技術を開発、2025年4月24日

<https://www.oki.com/jp/press/2025/04/z25006.html>

## ●筆者紹介

中條 靖太:Sota Nakajo. OKIサーフィットテクノロジー株式会社 上越事業所 技術本部 技術部

新保 靖行:Yasuyuki Shinbo. OKIサーフィットテクノロジー株式会社 上越事業所 技術本部 技術部

### CCL(銅張積層板)

絶縁性の基材(ガラスクロスなど)に樹脂を含浸させたシートを複数枚重ね、両面に銅箔を貼り付けて加熱・加圧することで作られるプリント配線板の主要材料。

### プリプレグ

ガラス繊維を一方向に引きそろえたシートまたは、織物に熱硬化性樹脂(主としてエポキシ樹脂)を含浸させて、乾燥させた成型品。

### 残銅率

プリント配線板の面積のうち、パターン部分(銅が残っている部分)の面積の割合を示す値。

### 積層ボイド

PCB積層において、プリプレグが層間に均一に充填されずにつ発生する空隙(ボイド)のこと。

### コプレーナ構造

伝送線路の両側面にリファレンス線路を加えた構造。

### ベタパターン

プリント配線板の空いているスペースを、GNDや電源といった広い面積の銅箔で塗りつぶすパターン。

## TIP【基本用語解説】

### PCB(高多層・高精細・大型プリント配線板)

絶縁体でできた板に表面や内部にパターンと呼ばれる導体の配線が施されたもの。

### HBM(High Bandwidth Memory)

次世代広帯域メモリー。複数のDRAMを積層し、専用の高速インターフェースを備える。

### DRAM (Dynamic Random Access Memory)

コンピューターや電子機器で広く使用される一時的なデータ保存用メモリー。電荷を保持するコンデンサーと、その電荷を制御するトランジスターで構成されたセルから成り、揮発性であるため、電源供給が停止するとデータが消失する特性を持つ。また、高速でデータの読み書きが可能で、大容量化に適している。たとえば、パーソナルコンピューター、サーバー、モバイルデバイスなどで利用される。