# $\mu$ PLATのプロトタイピング技術

稻葉 総一郎

近年、システムLSIは大規模化、微細化が進み、搭載されるソフトウェアも複雑になってきている。しかし、パソコン機器やモバイル機器等の組み込み機器の市場では、製品のライフサイクルが年々短縮している。このような背景から、短期間に品質の高いシステムLSIを開発することが大きな課題となっている。

弊社では、このように大規模化するシステムLSIの品質および設計生産性を向上させるためCPUプラットフォーム $\mu$  PLAT<sup>\*1)</sup>を提供している。 $\mu$  PLATはARM<sup>\*2)</sup> CPUを中心に、リアルタイムOSの動作に必要なメモリ制御、周辺IP (Intellectual Property), ソフトウェアおよび、プロトタイピングボードに代表される開発環境をプラットフォームとしてまとめたものである<sup>1)</sup>。

本稿では $\mu$  PLATプロトタイピングボードがシステムLSIの検証に有効な手段であることを示す。また、そこに使用されている技術について紹介する。

## 従来のシステムLSIの開発フロー

従来のシステムLSI開発フローでは、ハードウェア設計が完了し、サンプルLSI完成後（単体テスト後）に、実機を使用してソフトウェアを搭載し、システムLSI全体のシステム検証が行われていた。このような従来型のフローでは、サンプルLSI完成後でないとソフトを含むシステムLSIとしての本格的な検証ができないため全体の開発期間

が増加する。また、実機検証後にハードウェアのバグが発見されると、数千万円の再作成費用と、数ヶ月もの再設計期間を消費するだけでなく、市場機会を失ってしまう。

## ハードウェアとソフトウェアの協調検証

従来型フローにおける課題を解決するためには、サンプルLSIを製造する前の段階から、ソフトウェア(SW)とハードウェア(HW)の協調した検証を実施し、実チップにできる限り近い状態でのシステムレベルの検証を行うことが重要である。

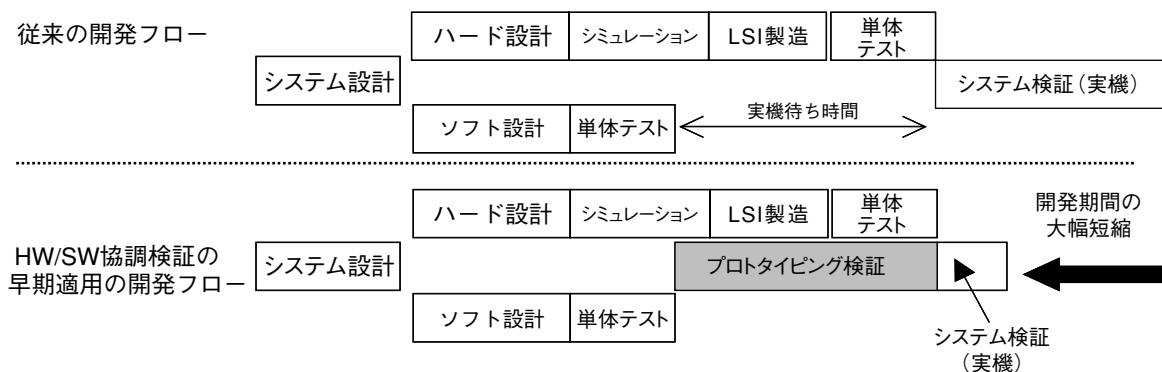

従来の開発フローとHW/SW協調検証を早期に適用するフローの例を図1に示す。

HW/SWの協調検証には、実チップに近い検証が可能なプロトタイピング検証と、サンプルLSIを使用した実機検証がある。

プロトタイピング検証はRTL (Register Transfer Level) 作成がある程度終了し、ハードウェアのタイミングを含めたシステムレベルの検証を実施できる段階である。この段階でのHW/SW協調検証は、実チップに近い検証が可能である。リアルタイムに動作すれば、実際の装置に組み込んだり、ネットワークや外部装置に直接接続したりし、実使用状態での検証が可能となり、システムとしての本格的な検証を実施できる。従来から、P

図1 システムLSI開発フロー

\*1)  $\mu$  PLATは沖電気工業(株)の登録商標です。 \*2) ARMはARM Ltd.の登録商標です。

ロトタイピング検証の段階で適用可能な手法として以下のような手法があった。

#### (1) エミュレータ

エミュレータは、RTLを専用の回路にマッピングしてハードウェア上で動作させることにより、シミュレータよりも高速な機能検証を実現できる。しかし、エミュレータは非常に高価であり、動作速度も論理シミュレータより向上しているとはいえ、高速動作が要求されるシステムLSIではリアルタイム動作が実現できないケースが多い。

#### (2) 専用プロトタイピングボード

FPGA (Field Programmable Gate Array) を搭載した専用プロトタイピングボードでは、RTLをFPGAにマッピングして、ソフトを含めたシステム検証を行うことができる。専用ボードのため、エミュレータより高速な検証環境を得ることはできるが、ボードをシステムLSIの開発ごとに設計するので、ボードの設計期間や開発費用が必要となる。また、新規にボードを起こすので、ボード自体の品質が安定しない段階で使用すれば、問題発生時に、LSIかボードかの原因切り分けのためデバッグ期間を増やすおそれがある。

#### (3) 汎用プロトタイピングボード

汎用のFPGAを搭載した、市販のプロトタイピングボードを利用してプロトタイピング検証を行うことも可能である。汎用プロトタイピングボードの場合、動作速度、ターゲットとするシステムLSIとの適合性、および価格などの点で、ユーザが満足できないケースが多い。

いずれの手法においても、動作速度、検証準備期間、コストの全ての要求条件を満足することは難しい。

#### **μPLATプロトタイピングボードの開発**

我々は、μPLATを用いたシステムLSIの開発のためにチューニングされたプロトタイピングボードを開発した。

μPLATプロトタイピングボードはμPLAT利用のシステムLSI開発のため最適にチューニングされている。したがって、μPLATを使用した実チップと極めて近い、リアルタイム動作可能な検証環境を低コストで提供できる。また、プラットフォームベース設計の利点を生かし、最小限の工数で容易にプロトタイピング検証環境を構築可能である。

μPLATプロトタイピングボードは、プロトタイピングボードに要求される下記の条件を満足している。

#### (1) リアルタイム動作（高速動作）

ネットワーク、無線、音声、画像処理等のシステムLSIではリアルタイム動作によるデバッグを行うことが検証の確度を向上させる上で非常に重要である。

#### (2) デバッグの容易性

ICE (In Circuit Emulator) などのデバッグポートおよび、FPGA内部の波形観測等が容易におこなえること。

#### (3) 検証環境立ち上げの容易性

プロトタイピング検証環境を短期間に、かつ容易に実現できること。

#### (4) 低コスト

開発期間を短縮するためにプロトタイピングボードを複数台同時に使用しても、全体の開発コストに対する影響が小さいこと。

表1にプロトタイピング検証方法の比較を示す。

μPLATプロトタイピングボードは、最も実チップに近い検証環境を短期間に、かつ低コストで提供できる。

表1 プロトタイピング検証手法の比較

|          | エミュレータ | 専用プロトタイピングボード | 汎用プロトタイピングボード | μPLATプロトタイピングボード |

|----------|--------|---------------|---------------|------------------|

| 動作速度     | △      | ◎             | ○             | ◎                |

| リアルタイム動作 | ×      | ◎             | ○             | ◎                |

| 検証準備期間   | ○      | ×             | △             | ◎                |

| コスト      | ×      | ×             | △             | ○                |

#### μPLATプロトタイピングボードを使用したシステムLSIの開発フロー

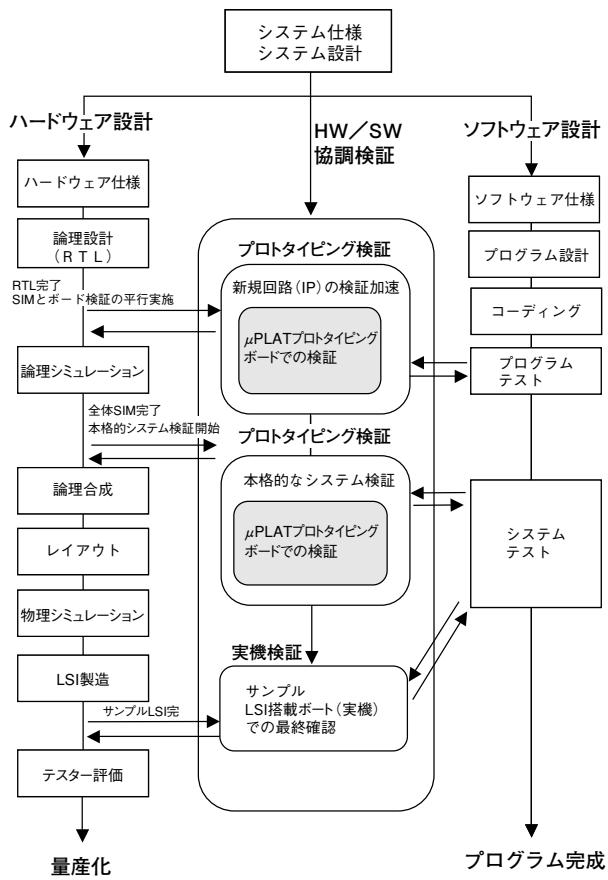

μPLATプロトタイピングボードを使用した場合のシステムLSIの開発フローを図2に示す。

ユーザは新規開発する回路(IP)のRTLが完成した段階で、単体シミュレーションとμPLATプロトタイピングボードによる検証とを平行に実施し、新規開発回路の品質を早期に高めることができる。次に、LSI全体の論理シミュレーションが終了した段階から、本格的なシステム検証を開始することができ、早期にLSIの完成度を高め、かつ、開発期間の大幅な短縮が可能となる。

図2 μPLATプロトタイピングボードを使用したシステムLSIの開発フロー

### μPLATプロトタイピングボードのアーキテクチャ

#### (1) ハードウェア構成

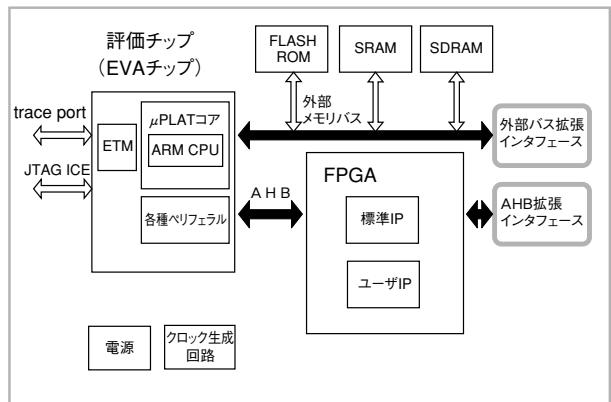

図3にμPLATプロトタイピングボードのハードウェア構成図を示す。

μPLATプロトタイピングボードは、ARM CPUを中心とした、μPLATコアにペリフェラルを搭載したμPLATの評価チップ（EVAチップ）、FPGA、メモリ、外部拡張インターフェース、クロック生成回路および電源等で構成される。FPGAにμPLAT標準IPやユーザが新規に開発するIPを搭載することにより、実チップと同じ論理を構成することができる。EVAチップとFPGAはARM社の標準バスであるAMBA<sup>③)</sup> AHB (Advanced High-performance Bus) によりインターフェースする。

#### (2) リアルタイム動作

LSI内部のオンチップバス（AHB）をボード上に構成する場合には、

- EVAチップのAHBバスの負荷容量、

- EVAチップとFPGA内のIOバッファー遅延、

- チップ間のクロックスキューリング

<sup>③)</sup> AMBAはARM Ltd.の登録商標です。 <sup>④)</sup> ETMはARM Ltd.の商標です。

図3 μPLATプロトタイピングボードハードウェア構成図

のため、チップ内と比べて、バス速度の低下は避けられなかった。

μPLATプロトタイピングボードでは、以下の手段を用いてオンチップバスと同等のバス速度をボード上で達成した。

- EVA-FPGA間を1対1接続とし、バスの負荷容量を低減した。

- EVAチップ内に、EVAチップ内部とEVAチップ外部のAHB動作クロック（HCLK）を分離するAHBtoAHBブリッジを搭載し、EVAチップ内部のバス信号遅延が、EVA-FPGA間のバス速度に影響を与えないようにした。

- クロック系統のスキューリング、動作電源電圧等の最適化を実施した。

- デバッグ系に関してもリアルタイムで、ARMコア内部バスをトレースできるARM社のETM<sup>④)</sup>（Embedded Trace Macro）を、EVAチップ上に搭載した。

これらの技術によりプロトタイピングボードの動作速度は実チップと同等に向上し、リアルタイム動作およびデバッグ機能が実現できた。

#### (3) デバッグポート

デバッグ用のポートとして、先に述べたETMの他に、JTAG ICE (In Circuit Emulator) を接続することができ、ソフトのデバッグを容易に実施できる。

ハード用デバッグインターフェースとしては、AHB等のモニターを行うため、ロジックアナライザコネクタや、各種観測用端子を搭載している。FPGA内部に関しては、内部回路観測用ポートを設けて、リアルタイムのFPGA内部波形観測を可能としている。

## (4) 検証環境立ち上げの容易性

$\mu$ PLATプロトタイピングボードでは、 $\mu$ PLATのコアの種別に対応するボード、およびFPGAに搭載する各種IPが準備されている。ユーザはLSIで適用する $\mu$ PLATコアに対応するボードと標準IPを選択し、ユーザが新規に開発するIPをFPGAに追加することにより、プロトタイピング検証環境を容易に構築することができる。

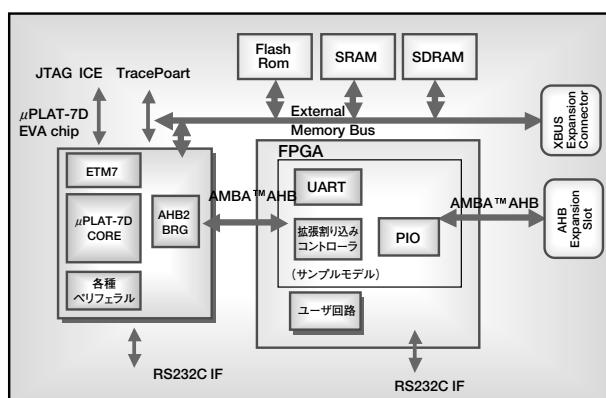

$\mu$ PLAT-7Dプロトタイピングボード概要

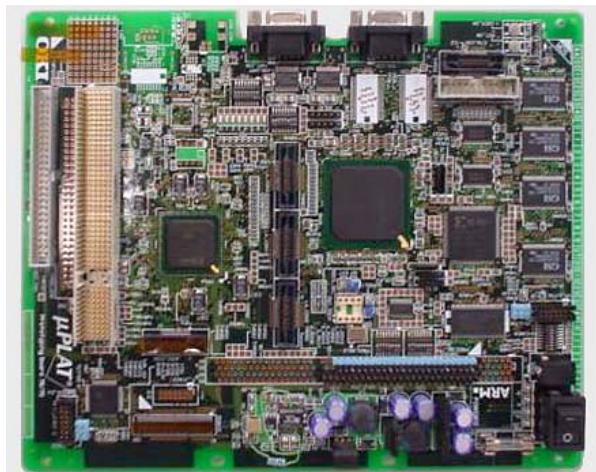

$\mu$ PLAT-7DプロトタイピングボードはARM社のARM7TDMI<sup>®\*5)</sup> CPUを搭載した $\mu$ PLAT-7Dコア、各種ペリフェラル、およびAHBtoAHBブリッジを実装した評価チップを搭載しており、ボード上のAHB動作速度は $\mu$ PLAT-7Dコアと同等となる。図4に $\mu$ PLAT-7Dプロトタイピングボードの構成図、諸元を表2に、写真を写真1に示す。

図4  $\mu$ PLAT-7Dプロトタイピングボード構成図写真1  $\mu$ PLAT-7Dプロトタイピングボード表2  $\mu$ PLAT-7Dプロトタイピングボード諸元

| 項目                    | 仕様                                                                                                                    |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------|

| CPU                   | ARM7TDMI                                                                                                              |

| 動作周波数                 | 80MHz                                                                                                                 |

| $\mu$ PLAT7D EVA Chip | ETM7、<br>ペリフェラル：<br>タイマ、DMAC、I2S、SSIO、<br>UART、ADC、PWM、WDT等                                                           |

| Memory                | 外部メモリバス(XBUS)拡張コネクタ<br>ROM: Flash 8MB<br>RAM: SRAM 3MB<br>DRAM: 16MB                                                  |

| Debug Support         | JTAG-ICE I/F<br>Trace Port Analyzer(ETM7)                                                                             |

| ユーザ拡張                 | FPGAをユーザ開放<br>搭載FPGA<br>ザイリンクス社XC2V500あるいは3000<br>AHB拡張コネクタ×1<br>AHB拡張用のFPGA搭載ボードをオプション<br>で用意<br>外部メモリバス(XBUS)拡張コネクタ |

| FPGAサンプルモデル           | 搭載IP<br>UART、PIO、拡張割り込みコントローラ等                                                                                        |

## むすび

本稿では、システムLSI開発における、プロトタイピング検証手法の比較を行い、 $\mu$ PLATプロトタイピングボードがシステム検証において有用であることを示した。また、 $\mu$ PLATプロトタイピングボードに使用される技術を概説し、 $\mu$ PLAT-7Dプロトタイピングボードを紹介した。

今後は、プロトタイピングボードに搭載されている、FPGAのサンプルモデルや、サンプルソフトウェアを充実させ、ユーザLSIからFPGAへの移植フローの更なる改善を進め、より使いやすい検証環境を整備していく予定である。

## ■参考文献

- 1) 来住、高塚、仲澤： $\mu$ PLATのハードウェア開発、沖電気研究開発184号、Vol.67 No.3、pp.45–48、2000年

## ●筆者紹介

稻葉総一郎：Soichiro Inaba、シリコンソリューションカンパニー デザイン本部 プラットフォーム設計部 サポートプラットフォームチーム

\*5) ARM7TDMIはARM Ltd.の登録商標です。