# 顧客が要求する多彩なバリエーションに応える P2ROM™商品技術

田坊 - 黒一郎

電子辞書やPDA等の携帯機器からプリンタなどの据置 き型機器に至るまで多くのシステムでROM(Read Only Memory) が使用されている。当社は顧客の要求する多彩 なバリエーションに応えるために、ROMの一種である P2ROM (Product Programmed ROM) 商品を提供し てきた。

#### P2ROMIA.

- ●マスクROM並みの低コスト

- ●コード受注から出荷まで2~3日の短TAT

という特徴を持っている。P2ROMが搭載される機器の高 機能化が進み、P2ROMに対する要求仕様が高度化してく ると、デザインルールの微細化による大容量化やアクセ ススピードの向上といった高性能化だけでは対応しきれ ないものもでてきた。そこで当社では、従来の汎用 P2ROMに加え、MCP (Multi Chip Package) 技術等 を利用した商品を開発した。

本稿では、当社のP2ROMの特徴と商品開発の取り組み について述べる。

### ROMの市場動向

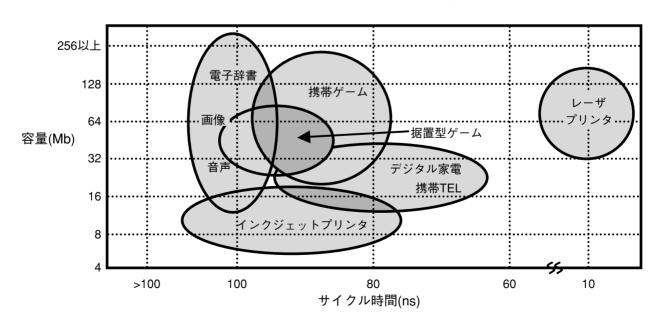

ROMの各種のアプリケーションに要求される容量およ びアクセス時間の関係は図1に示すようになっている。文 字や画像を取り扱うアプリケーションでは比較的低速だ が、大容量化が要求される。また、インクジェットプリ ンタやデジタル家電などのアプリケーションにおいては. 比較的低容量だが、高速性が要求される。さらに、レー ザプリンタなどのアプリケーションには、高速大容量が 要求される。大容量化への要求は、デザインルール、パッ ケージサイズで決まってしまう容量以上の要求も少なく ない。また、システムの高性能化やROMのコントロール 性の点から、従来の汎用ROMとは異なる方式のインタ フェースやコントロールの方法を用いたROMの要求も増 えている。加えて、高機能化、高性能化された新製品が 続々と登場するように機器のライフサイクルが短期間化 してきているため、ROMに対しても短期間に高性能化が 要求されるようになってきている。

以上の理由から、従来通りのデザインルールの微細化

図1 アプリケーション別要求仕様

#### P2ROMの優位性

P2ROMはEPROM (Electrically Programmable ROM) の一種であり、メモリセル内にフローティング ゲート構造を有する。FLASHに比べると簡単なセル構造であり、セルサイズも小さいためビットコストが低い。一方、マスクROMと比較すると、ウェハ工程や試験工程などの工程数が多く、セルサイズも大きいので単純にはビットコストが高い。しかし、以下の理由から、P2ROMはマスクROM並みの低コストを実現できる。

- ①読み出し機能に特化した回路構成と検査工程にするなどにより低コスト化が図れる。

- ②P2ROMは、チップサイズではマスクROMより大きいが、マスクROMには採用が難しい冗長救済技術を使用できるので歩留が高い。

- ③電気的にデータを書込むためデータ用のマスクが必要なく、コードマスク費用の顧客負担が不要である。

- ④未書込みROMを保管しておき必要な数量だけ書込み出荷できる。したがって、少量の要求にもコストが増えることなく対応できる。

大容量品では、0.16 μm以下のデザインルールによるセルの縮小化と救済率の高い冗長技術により、マスクROM以下の低コストにできる。また、あらかじめ未書込みROMを保管しておけば、コード受注後短TATで出荷できるため、海外のコストの低い工場で組み立てることができ、組立コスト比率が高い小容量品においても低コストとなる。

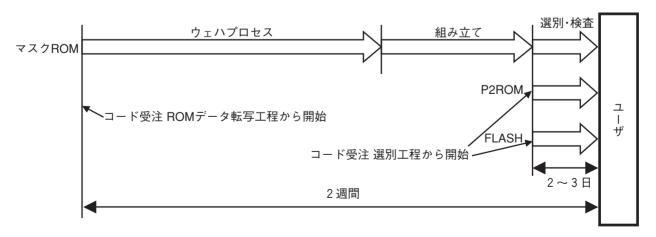

一方、TATの面ではマスクROMのようにウェハプロセスによってデータを書込むのではなく、出荷検査と同時にデータ書込みを行うため、コード受注から2~3日と

いう短納期で出荷が可能である。図2にマスクROMと P2ROMとFLASHのコード受注から出荷までのTATを 示す。

P2ROMは、大量生産時だけでなく、マスクROMには向かない開発用途や少量生産品への利用においても、短TAT、低価格で提供できる。メーカで書込んで出荷するFLASHはP2ROMと同等のTATが可能だが、チップコストが割高であるため、コスト面でP2ROMが有利である。

P2ROMは書換えができないが、多くのアプリケーションではROMデータの書換えは必要ではない。書換えが必要な顧客に対しても、書換え領域が小容量なら、大容量のP2ROMと小容量の書換え可能なROMを組合せることで、P2ROMに比べると高価なNOR型FLASHを用いる場合と同等な機能をより低コストで実現できる。

## 大容量化に向けた商品開発

大きなデータ量を扱う携帯機器のアプリケーションにおいては、実装面積の制約があるにも拘わらず、大容量ROMに対する要求が強い。現在、容量の面ではセルサイズの小さいNAND FLASHが有利であるが、NANDFLASHはもともとストレージ用デバイスであり、従来この分野で使用されてきたROMと異なってランダムアクセスができないという制約がある。またバッドセクタや不良ビットが存在するという欠点もある。アクセス方式の簡単なNOR型のほうが、顧客にとっては制御が容易で使いやすい。しかし市場の要求に応えるにはNANDFLASHにできるだけ近い大容量の商品を開発することが必要である

現在当社では $0.16 \mu m$ プロセスを使用した256Mb P2ROM (MR27V25603L: ノーマルモード, MR27V25653L: ページモード) を開発中である。これ

図2 コード受注から出荷までのTATの比較

表1 MR27V25603L/MR27V25653Lデバイス仕様

| 容量        | 256Mb                                        |  |

|-----------|----------------------------------------------|--|

| ビット構成     | $16\text{Mb} \times 16/32\text{Mb} \times 8$ |  |

| 動作電圧      | 2.7V~3.6V(MR27V25603L)                       |  |

|           | 3.0V~3.6V(MR27V25653L)                       |  |

| アクセス時間    | 120ns                                        |  |

| ページアクセス時間 | 30ns(MR27V25653Lのみ)                          |  |

| 動作時消費電流   | 35mA(MR27V25603L)                            |  |

|           | 60mA(MR27V25653L)                            |  |

| 待機時消費電流   | 10 μ Α                                       |  |

| パッケージ     | 50TSOPII                                     |  |

|           | 70SSOP                                       |  |

は $0.18 \mu$  mプロセスで開発した128Mb P2ROM (MR27V12800J) の2倍の容量である。表1に MR27V25603Lのスペックを示す。

現在、すでに256Mb以上の容量に対する要求も出てきている。現在開発中の0.16μmのデザインルールでは、従来のやり方で256Mbより大きい容量の商品を実現することは困難である。そこで、デザインルールによって決まる以上の大容量を実現するために、MCP技術を利用して複数のチップを1パッケージに搭載する方法を採用した。現在この方式を利用した商品として128Mb P2ROM (MR27V12800J: ノーマルモード、MR27V12850J: ページモード)のチップ2個を1パッケージに搭載した256Mb P2ROM (MR26V25605J, M26V25655J)を量産中である。MR26V25605JはMR27V12800Jを表裏に実装し、またMR27V12800Jと異なるピン配置であるため、それぞれのチップにピン配置を変換するチップを使用した4チップのMCPである。表2にスペックを示す。

また、 $0.16 \mu$ mデザインルールを用いた256Mb P2ROM (MR27V25603L) の開発と同時に、このチップを1パッケージに2個を搭載した512Mb P2ROM

表2 MR26V25605J/MR26V25655Jデバイス仕様

| 容量        | 256Mb                                    |  |

|-----------|------------------------------------------|--|

| ビット構成     | $8\text{Mb}\times32/16\text{Mb}\times16$ |  |

| 動作電圧      | 3.0V~3.6V                                |  |

| アクセス時間    | 90ns(MR26V25605J)                        |  |

|           | 120ns(MR26V25655J)                       |  |

| ページアクセス時間 | 30ns(MR26V25655Jのみ)                      |  |

| 動作時消費電流   | 60mA(MR26V25605J)                        |  |

|           | 100mA(MR26V25655J)                       |  |

| 待機時消費電流   | 50 μ A                                   |  |

| パッケージ     | 70SSOP                                   |  |

表3 MR26V51203L/MR26V51253Lデバイス仕様

| 容量        | 512Mb                            |  |

|-----------|----------------------------------|--|

| ビット構成     | 32Mb×16/64Mb×8                   |  |

| 動作電圧      | $2.7 \text{V} \sim 3.6 \text{V}$ |  |

| アクセス時間    | 120ns                            |  |

| ページアクセス時間 | 30ns                             |  |

| 動作時消費電流   | 40mA(MR26V51203L)                |  |

|           | 80mA(MR26V51253L)                |  |

| 待機時消費電流   | $20\mu\mathrm{A}$                |  |

| パッケージ     | 50TSOPII                         |  |

|           | 70SSOP                           |  |

(MR26V51203L:ノーマルモード、MR26V51253L:ページモード)の開発も行っている。MR27V25603LのチップはMR26V51203Lの開発を前提に設計されておりMCP専用インタフェースを構えている。MCP専用インタフェースを搭載することでピン配置を変換するチップを使用せずにMR27V25603Lとビット構成やピン配置の互換性が確保できる構成になっている。チップを積層搭載し、変換チップも不要であるため薄型パッケージも実現できる。表3にMR27V51203Lスペックを示す。

今後はさらに進んだデザインルールでは、256Mbあるいは512Mbチップを2枚以上積層したギガビットクラスの商品展開も考えている。

## カスタム仕様に向けた商品開発

従来、インタフェースやコントロールの方法が汎用とは異なる仕様の場合には専用のチップを設計する必要があった。これを1チップで実現する場合、メモリ部分を含めた回路設計とレイアウト設計、およびそれぞれの検証が必要となり、開発に長い期間を必要とする。開発コストおよび設計TATの面からカスタム仕様の要求に対応することが困難であった。しかし、MCP技術を利用して、汎用P2ROMチップとインタフェースなどの機能を持ったチップを組合せることで、カスタム仕様のP2ROMを低コスト、短期間で実現することが可能となった。機能チップはP2ROMと外部とのインタフェースの役割を果たし、パッケージされたデバイスは外観上メモリデバイスとして機能する。この方式を利用すると、以下の理由から短期間での商品開発、サンプル出荷が可能になる。

- ①機能チップの開発は特性が既知のメモリチップに合わせて設計と検証を行うことができる。

- ②機能チップはメモリを含まないインタフェース機能だけの役割なので、回路規模が大きくなく短期間で設計できる。

|    |                 | 2003年 | 2004年            | 2005年                      |  |

|----|-----------------|-------|------------------|----------------------------|--|

|    | 0.13 μ m        |       |                  | .:<br>512Mbを開発予定           |  |

|    | 0.15 μ m        |       |                  | 低電圧・多機能、1Gb (MCP)<br>を開発予定 |  |

| デザ | 0.16 <i>μ</i> m |       |                  | 512Mb (dual die)           |  |

| ザ  |                 |       |                  | 256Mb                      |  |

| ルー | 0.17 μ m        |       |                  | 128Mb                      |  |

| ル  |                 |       |                  | 64Mb                       |  |

|    | 0.18 μ m        |       | 256Mb (dual die) |                            |  |

|    |                 |       | 128Mb            |                            |  |

|    |                 |       | 32Mb             |                            |  |

図3 P2ROM ロードマップ(小容量品は除く)

この方式は、シリアルインタフェース、アドレス-出力 共通ピンインタフェース、あるいは独自のコントロール 機能(同期式、コマンド入力方式など)といった広範な 目的に応用が可能である。

#### 今後の開発

当社では、これまで述べてきた方法を利用して顧客のさまざまなニーズに対応できるよう商品開発を行い、P2ROM商品ラインアップの充実を目指している。加えて、システムのライフサイクルの短縮化に伴うROMの高性能化の要求に短期間で対応することができるように、デザインルールの更新サイクルの短期間化をはかっている。図3に汎用P2ROMのロードマップを示す。近年、多値FLASHの登場によりP2ROMのコストアドバンテージが縮まりつつあるが、これに対応するため、新規メモリセル方式の開発等、技術革新を図り、さらに高性能、低コストなP2ROM商品の実現に向けて努力を続けていく。◆◆

## ●筆者紹介

武田景一郎: Keiichiro Takeda.シリコンソリューションカンパニー デザイン本部 P2ROM設計部