# 高速カラープリンタコントローラ ハードウェア

石川 修 井伊 昭一

近年、デジタルカメラやインターネットの普及と共にオフィスでのカラー化は急速に増加、浸透している。カラー印刷されたプレゼンテーション資料を入手することも珍しくなくなってきている。これに伴いカラー印刷を高速に手軽に印刷できることが市場から求められている。沖データは高速化のためシングルバスカラー®\*1)方式(タンデム方式)を用いた高速カラープリンタを提供している。Y(イエロー)、M(マゼンダ)、C(シアン)、K(ブラック)の4色同時印刷を行うシングルバスカラー®の特徴を生かすべく画像データを生成するコントローラも各色ごとに適切な処理が要求される。また、4色を同時処理するため、各色を4回シリアルに重ねて印刷を行う4パス方式と比べて約4倍のデータ処理能力が必要とされる。

本稿では、カラープリンタコントローラハードウェアの動向、および沖データが提供しているシングルパスカラー®方式のカラープリンタコントローラハードウェアをハイエンドコントローラ、ローエンドコントローラの観点からその概要と構成について紹介する<sup>1) 2)</sup>。

# カラープリンタコントローラ市場動向

#### (1) タンデム方式と4パス方式

4パス方式のプリンタはY→M→C→Kのように順次各色の印刷が行われるので、コントローラは同時には1色分のデータを処理する能力があれば良い。一方タンデム方式ではY, M, C, Kの4色が同時に印刷されるため、コントローラは同時に4色のデータ処理を行う必要がある。コントローラではCPUが中心となってデータ処理行うため、CPUの動作周波数がコントローラのパフォーマンス(処理能力)を計る指標の一つとして考えられる。他にもメモリとのデータアクセス能力を表すメモリバンド幅や、ASICで実現する画像処理、インタフェースの受信能力等の指標がある。

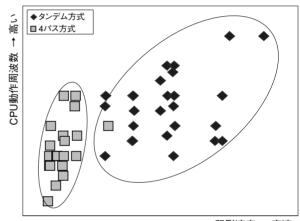

図1は最近発表された各社プリンタのCPU動作周波数とカラー印刷速度の関係をプロットしたものであり、タンデム方式と4パス方式で分類してある。4パス方式は印刷速度が低速のものに集中して発表されており、高速プリ

\*1) シングルパスカラーは株式会社沖データの登録商標です。

ンタのほとんどはタンデム方式となっている。また、図1から4パス方式よりタンデム方式のプリンタに使用されているCPUの動作周波数が高く、印刷速度が速くなるのに応じて使用されるCPUの動作周波数も高くなる傾向にあることが理解できる。

印刷速度 → 高速

図1 印刷方式とCPU動作周波数および印刷速度の関係

#### (2) 印刷言語種類とコントローラの関係

プリンタはPC等のホストコンピュータからPostScript, PCL等のページ記述言語(PDL: Page Description Language)で記述された印刷データを受信し、ビットマップのデータに変換して印刷を行う。この印刷データからビットマップデータへの変換作業がコントローラのまな機能であり、コントローラのパフォーマンスも変換作業を高速に行うことに注力している。一方、PC等に採用されるCPUも3GHzを越える動作周波数のものが発表されており、PCの処理能力の向上が見られる。この動作環境変化に伴い印刷データからビットマップデータへの変換作業をホストコンピュータ側で行い、生成されたビットマップデータをプリンタに送り、プリンタは受信したビットマップデータをそのまま印刷するホストベース方式のカラーページプリンタも発表されている。パフォーマンスが要求される変換作業をプリンタ側で行う必要が

ないので、プリンタコントローラを単純化でき、低価格が比較的容易に実現できる。

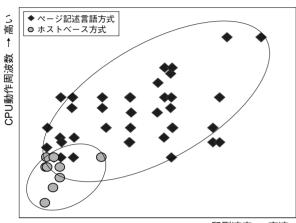

図2は、図1の関係をホストベースプリンタとページ記述言語を採用するプリンタに分類したものである。コントローラにパフォーマンスが要求されないため、同じ印刷速度のプリンタであっても動作周波数の低いCPUがホストベースプリンタに採用されていることが理解できる。

印刷速度 → 高速

図2 印刷言語種類とCPU動作周波数および印刷速度の関係

# ハイエンドカラープリンタ コントローラハードウェアの紹介

# (1) ハイエンドカラープリンタコントローラ概要

高速・高解像度を実現したハイエンドカラープリンタ はホストコンピュータに負荷をかけず独立性を保持する ためページ記述言語が採用されている。インタフェース から受信され、ページ記述言語で記述された印刷データ に応じて編集処理・展開処理が行われ、Y, M, C, Kの ビットマップデータが各色同時に生成される。編集処理 では、印刷データを展開し易いフォーマットに変換し中 間データを生成する。展開処理では中間データを描画命 令としてビットマップデータの重ね書き等を行い最終的 なビットマップデータを生成する。これら一連の処理に CPUパワーが最も必要とされる。動作周波数の高いCPU が使用されるのも、これらの処理を高速に行うためである。 一方、圧縮・伸長や色変換処理、ディザ等に代表される2 値化処理は処理内容が比較的単純なアルゴリズムなので ASICで実現される場合が多い。ASICで実現した機能は CPUで処理した場合に比べ数倍の処理速度が達成可能で ある。

#### (2) ハイエンドカラープリンタコントローラ構成

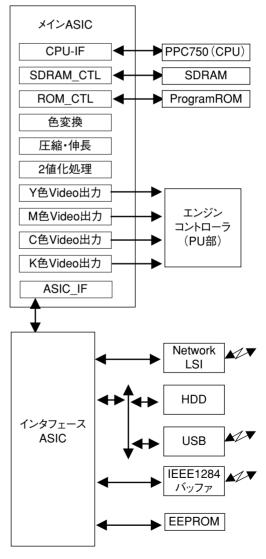

図3はハイエンドカラープリンタコントローラハードウェアの機能ブロック図である。CPUからのメモリアクセスおよびASICで実現した画像処理モジュールからのメモリアクセスによる大量のデータアクセスが滞りなく行われるように、ASIC内部バスおよびSDRAMコントローラの開発を行っている。CPUの命令が格納されているProgram ROMへのアクセスとSDRAMへのアクセスが並行して行えるよう、Program ROMへのデータバスとSDRAMへのデータバスは別々に設けた。ASICで実現した画像処理機能およびエンジンコントローラへビットマップデータを出力するVideo出力部は処理能力と回路規模を検討・評価し、必要に応じて複数回路を設けた。CPUに関しては、動作周波数、キャッシュサイズ、外部とのデータアクセスを行うFSB(Front Side Bus)能力およ

図3 ハイエンドカラープリンタ機能ブロック図

びASICで実現した機能に応じてCPU処理が軽減されることを考慮し、システムとしてパフォーマンスが最大限発揮できるCPU選択と設定を行っている。インタフェースに関しては10Base-T/100Base-Tx, USB, IEEE1284を実現し、動作環境への適応力を持たせている。また、IEEE1394、IEEE 802.11a/b/g等の無線LAN、Gigabit Ethernetはニーズに合わせた提供が必要である。

CPUとASIC間、ASICとSDRAM間等のデータ転送速度も100MHz以上が実現されてきており、CPUやASICを実装する基板における配線パターンの配置が重要な技術となってきている。ASICの端子配置やI/Oパッファタイプを決定する前に仮想配線パターンを引き、IBIS(I/O Buffer Information Specification)モデルによる基板シミュレーションにより最適な端子配置やI/Oパッファタイプを選定し、配線パターンの配置を充分検討する必要がある。今後市場において、PCI Express™\*2)、HyperTransport™\*3)、RapidIO™\*4)等の高速シリアルバスが広まる可能性があり、数百MHz~数GHzの転送速度を基板上で実現する技術が必要となってくる。

# ローエンドカラープリンタ コントローラハードウェアの紹介

#### (1) ローエンドカラープリンタコントローラ概要

高速・低価格を実現したローエンドカラープリンタは、ビットマップ化をPC側で行うホストベース方式が採用されている。この方式では、PC側のプリンタドライバでY、M、C、Kのビットマップデータの生成と、データの圧縮処理が行われ、プリンタへ送出される。一方、コントローラはインタフェースからそのデータを受信し、伸張処理を行い、再びY、M、C、Kのビットマップへ復元し印刷を行う。このように、最もCPUパワーを必要とするビットマップデータの作成をPC側に分担させることで安価なCPUを使用することが可能である。この方式のコントローラ性能は、受信性能、伸長性能で決定される。

#### (2) ローエンドカラープリンタコントローラ構成

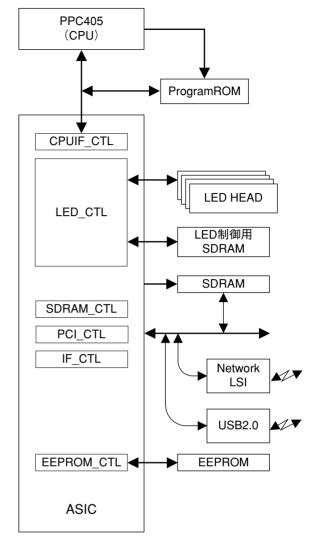

図4はローエンドカラープリンタコントローラハード ウェアの機能ブロック図である。

低価格化のため、ASICを1つに集約し部品点数の削減を行っている。ハイエンドコントローラのASICと比較すると、SDRAMとNetwork LSI、USB LSIのデータバスの共用化やバス幅の縮小(32bit化)を行うことで外部ピンを削減したASICを実現している。インタフェースは、受信性能を重視し、低速なIEEE1284は搭載せず、10Base-T/100Base-Txの他に、High Speed USB2.0

図4 ローエンドカラープリンタ機能ブロック図

を搭載した。PCからの受信データの圧縮・伸張アルゴリズムには、圧縮効率の高いJBIGを採用し、高速なインタフェースと組み合わせることにより、PC側で作成したビットマップを高速に受信し処理することを可能としている。また、従来エンジンコントローラ(PU部)にあったLEDヘッド制御回路は専用ASICで実現していたが、図4のLED\_CTLモジュールで示すように一つのASICに統合し、部品点数を削減し、低価格化を行っている。

更なる性能アップの方策として、ASICの高速化の他に、ネットワーク処理や伸張処理をハード化することが検討されている。ただし、ASICの高速化は、ASICの価格アップに繋がる場合がある。ローエンドプリンタコントローラに関しては、プリンタのエンジンスピードに合わせる適切な設計が重要視される。低価格化の方策としては、既にLEDヘッド制御回路の取り込みを行っているが、PU側

\*2) PCI Express はPCI-SIGの商標です。 \*3) HyperTransportはHyperTransport Technology Consortiumの商標です。 \*4) RapidIOはRaidIO Trade Associationの商標です。

のCPU、モータ制御回路等の取り込みが課題となる。

ホストベース方式は、PCの性能が高ければより快適になり、低すぎると快適性が低下する場合がある。よってページ記述言語を実行可能なコントローラを、ホストベース方式と同程度のコストで如何に実現するかが課題となっている。

# カラープリンタコントローラハードウェアの今後

カラープリンタは、今後高速化と高解像度化が進み、必要とされる画像処理機能も高度化されることが予想される。このためコントローラハードウェアに要求されるパフォーマンスも更なる向上が求められる。一方、市場は低価格化が進み、手軽さが要求される。これらの要求に対しパフォーマンスと価格のバランスの取れたコントローラハードウェアの提供が重要である。

### (1) 高速化の追求

コントローラパフォーマンスはCPU、メモリ、ASICが主要因である。特に、CPUとのインタフェース、メモリとのインタフェースおよび画像処理を実現するASIC機能がコントローラ全体のパフォーマンスを決定すると言っても過言でない。

CPUは動作周波数のパフォーマンス指標で評価される場合が多いが、CPUが外部とアクセスするFSBのバンド幅能力が重要であり、CPU要因のパフォーマンスを上げるため、今後数Gbyte/secの高速FSBに対応したASICを開発する必要がある。FSBのバンド幅能力を向上させることにより、CPU動作周波数の向上がパフォーマンスに寄与する割合を高めることが可能である。

CPUのFSBのバンド幅能力の向上と共に、メモリのバンド幅能力の向上が必要である。現在PCで使用されているDDR(Double Data Rate)-SDRAMやその後継とされているDDR-Iの数Gbyte/secのメモリバンド幅を実現するメモリコントローラを取込んだASICの開発が必要である。

#### (2) 低価格化の追求

コントローラコストは、CPU、ASIC、SDRAM等のRAM、Program ROM、ネットワークに代表されるインタフェース等に分類して検討することができる。これらの要因においてCPUとASICの価格がコントローラコストの大きな割合を占めており、ローエンドコントローラにおいてCPUとASICの低価格化が大きな課題である。

近年の半導体プロセスの進歩により、数メガゲートの ASICの実現が可能になってきており、従来、機能ごとに 個別ASICで実現していた機能を一つのASICで実現することや、CPUをASICに取込むことによる低価格化の検討が必要となってくる。

以上,高速カラープリンタコントローラをハードウェアの観点から説明した。当社の高速カラープリンタをより高速に手軽に使える商品として提供するために,ハイパフォーマンスかつ低価格なコントローラハードウェアを目指して開発を行っていく。 ◆◆

# ■参考文献

1) 長田昌登, 西山由高, 伊東和彦: 沖テクニカルレビュー185号, シングルパスカラー<sup>™</sup>プリンタの高速コントローラ技術, Vol.68 No.1, pp.128-131, 2001年1月

2) 石川英次, 吉田伸廣, 長田昌登, 吉本斉裕, 佐藤晋: 沖電気 研究開発178号, カラー電子写真プリンタコントロール技術, Vol.65 No.2, pp.23-28, 1998年5月

# ●筆者紹介

石川修: Osamu Ishikawa.株式会社沖データ コントローラ開発 センタ ハードウェア開発部 部長

井伊昭一: Shoichi Ii. 株式会社沖データ コントローラ開発センタ ハードウェア開発部 チームリーダ