# システムLSIのテスト容易化設計手法

牛久保 政憲

システムLSIは、ロジックコア、メモリコア、アナログコア等が搭載された大規模回路であることから、LSIの機能テストで十分なテスト品質を確保することが課題である。そこで、当社では、テスト品質向上およびテスト設計TAT(Turn Around Time)低減を目的に、テスト容易化設計手法を適用している。一方では、近年、微細化とともに、搭載コア数および回路規模がいちじるしく増加しており、テスト時間の増加が問題となっている。

我々は、システムLSIのテスト時間を50%以上低減するテスト容易化設計手法を支援する設計自動化ツールを開発・導入した。本ツールは、テスト時間を低減するだけでなく、テスト容易化設計手法適用時に弊害となる、チップ面積増加、消費電力増加、およびスピード低下を抑止する機能と、テストピン数を最適化する機能も有している。本稿では、テスト時間を低減するテスト容易化設計手法、本手法を実現するために開発・導入した設計自動化ツールと設計フロー、およびテスト時間低減効果について述べる。

# テスト時間を低減するテスト容易化設計手法

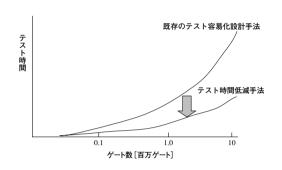

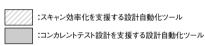

図1に示すように、システムLSIにおけるテストの課題としては、回路規模の増加とともにテスト時間が増大することである。我々は、システムLSIのテスト品質を低下させることなく、テスト時間を低減することを目的とした手法を、既存のテスト容易化設計手法に対して、機能拡張を図ることで実現し(表1)、50%以上の低減を可能とした(図1)。以下に、その二つの手法(1)スキャン効率化と(2)コンカレントテスト設計について述べる。

## (1) スキャン効率化

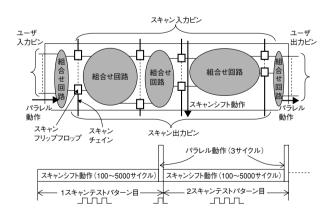

スキャン<sup>1)</sup> とは、回路内部のフリップフロップ(以降、スキャンフリップフロップと呼ぶ)をピンから直接制御・観測する経路(以降、スキャンチェインと呼ぶ)を付加して、テストパターンの生成を容易にする手法である。スキャン回路とスキャンテスト手順を、図2に示す。

スキャンテスト動作は,スキャンフリップフロップを スキャン入力・出力ピンから直接制御・観測するために

図1 ゲート数VSテスト時間

表1 テスト容易化設計手法

| テスト容易化設計手法 | テストの対象                          |       | ニュいは関係は毛汁   |

|------------|---------------------------------|-------|-------------|

|            | 回路                              | テスト項目 | ・テスト時間低減手法  |

| フルスキャン     | ランダムロジック、ロジッ<br>クコア             | 機能テスト | スキャン効率化     |

| メモリBIST    | メモリコア                           | 機能テスト | コンカレントテスト設計 |

| 分離テスト      | ロジックコア (非スキャン)、<br>メモリコア、アナログコア | 機能テスト | コンカレントテスト設計 |

図2 スキャン回路とスキャンテスト手順

スキャンチェインを動作させるスキャンシフト動作と、組合せ回路をユーザ入力・出力ピンから制御・観測するパラレル動作からなる。スキャンテスト手順は、スキャンシフト動作とパラレル動作の繰り返しとなり、この繰り

返し回数がスキャンテストパターン数である。スキャン 回路の全テストサイクル数(以降、スキャンテストサイ クル数と呼ぶ)は、等価的にスキャンテストパターン数 とスキャンシフトサイクル数の積となる。したがって、ス キャンテストパターン数またはスキャンシフトサイクル 数を削減することにより、スキャンテストサイクル数を 削減でき、テスト時間低減を実現できる。

我々は、スキャンテストパターン数およびスキャンシフトサイクル数を削減するための回路を生成する設計自動化ツールを開発・導入した。本スキャン回路の適用により、テスト品質を低下させずにスキャンテスト時間を低減できる。なお、スキャン対象回路は、ランダムロジックおよびスキャン化可能なロジックコア(以降、スキャンコアと呼ぶ)となる。

# (2) コンカレントテスト設計

コンカレントテストとは、LSIに搭載されている複数のコアおよび回路を並列にテストする手法である。

スキャン化不可能なロジックコア(以降,非スキャンコアと呼ぶ)とメモリコアの機能テスト時間を低減するために,これらのコアに対しては,既存のメモリBIST (Built-In Self-Test)<sup>2)</sup> および分離テスト手法に,コンカレントテストを実現する。また,コアだけではなく,スキャンコアおよびランダムロジックを合わせたスキャン回路に対しても,非スキャンコアおよびメモリコアと,コンカレントテストを実現する。

我々は、コンカレントテスト用に、メモリBIST回路および分離テスト用回路(コアをピンから直接制御・観測するための回路)を生成する設計自動化ツールを開発・

導入した。本テスト回路の適用により、テスト品質を低下させずにテスト時間を低減できる。また、コンカレントテストを実現するためのテストパターンを生成するツールも開発・導入した。

# スキャン効率化を支援する設計自動化ツール

スキャン効率化のために、スキャンテストパターン数 削減回路挿入ツールおよびスキャンチェイン平均化ツールの2つの設計自動化ツールを開発・導入した。

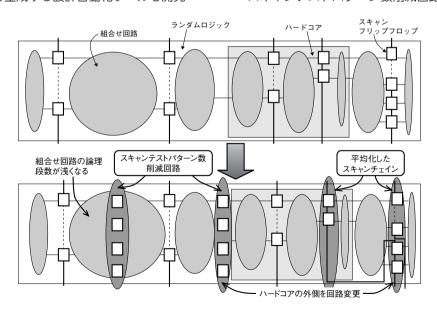

図3に、これらのツールを使用して生成する、スキャン 回路のイメージ図を示す。

各ツールの主な機能を、以下に述べる。

# (1) スキャンテストパターン数削減回路挿入ツール

本ツールは, 既にスキャン化した回路に対して, スキャンテストパターン数削減回路を組合せ回路の論理段数の深い箇所に挿入する。

# ● ハードコア内部の考慮

ハードコア内部と他のスキャン回路(ランダムロジックや他のスキャンコアなど)間での組合せ回路の論理段数が深い場合には、スキャンテストパターン数削減回路を、ハードコア外部に挿入する(図3)。

# ● チップ面積増加抑止

スキャンテストパターン数削減回路のゲート規模を指定することによって、チップ面積の増加を抑止できる。ただし、指定しないで実行しても、ゲート数の増加は1%程度である。

## ● スピード低下抑止

スキャンテストパターン数削減回路はセル間のネット

図3 スキャン効率化を実現する回路イメージ図

に挿入されるのではなくネットに接続されるだけなので. 本ネットのファンアウト数がひとつ増加するだけで済み, システムのスピード低下への影響は少ない。

## ● 消費電力増加抑止

スキャンテストパターン数削減回路の動作を停止させ るための回路を挿入することで、消費電力増加を抑止で きる。

#### (2) スキャンチェイン平均化ツール

本ツールは、スキャンシフトサイクル数削減を実現す るツールである。スキャンシフトサイクル数は、1チェイ ン当たりの最大スキャンフリップフロップ数である。し たがって、各スキャンチェインのスキャンフリップフロッ プ数を平均化することにより、スキャンシフトサイクル 数を削減できる。本ツールは、既にスキャン化した回路 に対して、スキャンチェインを平均化するために、スキャ ンチェインを再構築する。

# ● ハードコア内部の考慮

ハードコア内部のスキャンチェインも、他のスキャン 回路に含めて平均化する(図3)。

● マルチクロックへの対応

異なるクロック系のスキャンフリップフロップを同一 チェインにする場合、タイミング問題を起こさないため の回路を挿入する。

# コンカレントテスト設計を支援する設計自動化ツール

各種コアのコンカレントテストを実現するために、メ モリBIST回路およびBIST起動テストパターン生成ツー ル、メモリBIST回路および分離テスト用回路挿入ツール、 およびコンカレントテスト用パターン生成ツールの3つの 設計自動化ツールを開発・導入した。

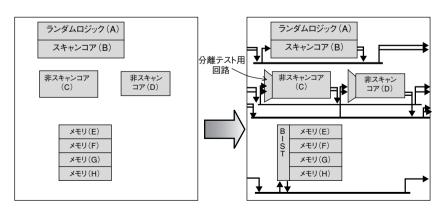

図4に、これらのツールを使用して、コンカレントテス ト用メモリBIST回路および分離テスト用回路を挿入した 回路イメージ図を示す。

各ツールの主な機能を、以下に述べる。

# (1) メモリBIST回路およびBIST起動テストパターン生成

本ツールは、メモリのワード・ビット構成を指定する ことにより、コンカレントテストを実現するRTL (Resister Transfer Level) 記述のメモリBIST回路を生 成すると共に、BIST回路を起動するテストパターンを生 成する。

#### ● 各種構成のメモリコアに対応

異なるワード・ビット構成を有する複数メモリコアに 対しても、コンカレントテストを実現するBIST回路の生 成が可能である。

#### ● 消費電力増加抑止

システム動作時に、BIST回路動作を停止させる回路を 挿入する。

- (2) メモリBIST回路および分離テスト用回路挿入ツール RTL記述の回路に、メモリBIST回路および搭載コアを コンカレントにテストするための分離テスト用回路を挿 入する。

- チップ面積増加およびスピード低下抑止

RTL記述の回路にテスト用回路を挿入することで、シ ステム回路と同時に論理合成可能で、チップ面積および スピードの最適化が図れる。

#### ● 消費電力増加抑止

複数コアを動作させることによる消費電力増加を考慮 して、特定コアに対してシーケンシャルテストのための 分離テスト用回路を挿入できる。

## ● テストピン数の最適化

非スキャンコアの総端子数とメモリBIST端子数の合計 が、LSIピン数以下に収まる範囲内で、コンカレントテス トのための分離テスト用回路を挿入する。

(3) コンカレントテスト用パターン生成ツール 本ツールは、メモリBIST起動テストパターン生成ツー

図4 コンカレントテストを実現する回路イメージ図

ルが生成したテストパターン、非スキャンコアのテストパターン、およびスキャンテストパターンを入力として、挿入したテスト用回路の結線情報を元に、パターン編集を行い、コンカレントテスト用パターンを生成する。なお、非スキャンコアのテストパターンに関しては、コア設計者から供給され、スキャンテストパターン生成ツールで生成される。

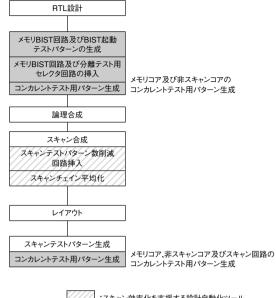

# テスト時間低減設計自動化ツールを使用する設計フロー

開発・導入した設計自動化ツールを使用する設計フローを図5に示す。網掛けで示されているところが、開発・導入したツールであり、従来の設計フローを変更することなく容易に適用できる。

テスト設計TATに関しては、スキャン効率化作業が、従来のスキャン設計に対して新たに必要となる設計作業であるが、2つの設計自動化ツールを使用することで、1日程度の増加で済む。また、コンカレントテストについては、3つの設計自動化ツールを使用することで、従来人手で1~2週間要していた設計作業が、2日以内で実現可能となる。

# テスト時間低減の効果

開発・導入した手法によるテスト時間低減効果を図6に示す。スキャン効率化により、スキャンテスト時間を半減することが可能である。図6での、ランダムロジック(A)とスキャンコア(B)のテスト時間を半減できる。ランダムロジック(A)とスキャンコア(B)を合わせたスキャン回路、非スキャンコア(C)、非スキャンコア(D)、およびメモリコアに対しては、テストピン数などを考慮してコンカレントテストすることで、機能テスト時間を低減できる。スキャン効率化およびコンカレントテストを組み合わせて適用することにより、50%以上のテスト時間低減が可能である。

### あとがき

我々が適用したテスト容易化設計手法は、スキャン回路、メモリBIST回路、分離テスト用回路に工夫を施す手法であり、システムLSIのテスト品質を低下させずにテスト時間を半減させることが可能である。また、本手法を実現するために開発・導入した設計自動化ツールは、テスト容易化設計手法適用時懸念される問題点を抑止する機能を有しており、システムLSIに適用しやすくなっている。さらに、開発したツールは既存の設計フローと親和性が高くテスト設計TATを増加させることはない。

開発手法、ツールはすでに実設計で運用されており、成

図5 テスト時間低減設計自動化ツールを使用する設計フロー

図6 テスト時間低減効果

果を上げている。今後は、さらなるテスト時間低減に取り組んでいく。 ◆◆

## ■参考文献

1) 畠山: 設計者に必要なテスト容易化設計の基礎知識, デザインウエーブマガジン, pp.47-54, March, 2001年

2) 佐藤:設計者に必要なBIST技術の基礎知識, デザインウエー プマガジン, pp.55-67, March, 2001年

# ●筆者紹介

牛久保政憲: Masanori Ushikubo. シリコンソリューションカンパニー LSI事業部 テスト技術部